Articles

IEEE Design&Test publication information

Presents a listing of the editorial board, board of governors, current staff, committee members, and/or society editors for this issue of the publication.

Read more...Special Issue on "Verification and Test "

This issue is focused on the special issue on “Emerging Challenges and Solutions in SoC Verification” from Guest Editors Magdy Abadir, Jayanta Bhadra, Wen Chen, and Li-C Wang. This special issue on verification is very timely, as new developments demand new verification techniques. For instance, the increasing heterogeneity of on-chip-...

Read more...Guest Editors' Introduction: Emerging Challenges and Solutions in SoC Verification

Verification has been one of the major bottlenecks in integrated circuit design process, which is exacerbated by the sheering design complexities nowadays. The increased design size is only one dimension of the growing complexities. Recent System-on-Chips (SoC) often feature multiple heterogeneous embedded processors and accelerators. ...

Read more...Challenges and Trends in Modern SoC Design Verification

This paper provides a tutorial overview of the state-of-the-art in verification of complex and heterogeneous Systems-on-Chip. The authors discuss current industrial trends and key research challenges.

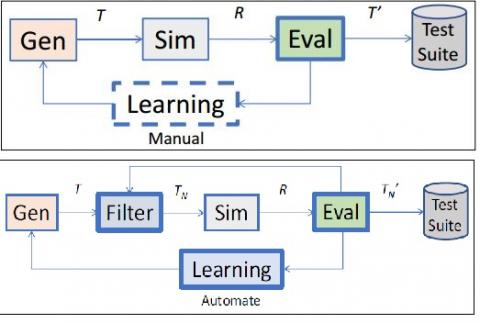

Read more...Data-Driven Test Plan Augmentation for Platform Verification

This article points out that the fundamental problem of platform verification is incompleteness of the test plan and proposes an unsupervised learning approach to augment the test plan.-Magdy Abadir, Helic Inc.

Read more...Formally Verifying Transfer Functions of Linear Analog Circuits

This article presents an approach to extend mathematical formal analysis towards verification of linear analog circuits.

Read more...Embedded Systems Secure Path Verification at the Hardware/Software Interface

The article presents a case study comparing two types of properties for formal verification of security requirements in embedded systems.

Read more...Leveraging Software Configuration Management in Automated RTL Design Debug

This article presents an enhancement to the existing automated debugging software by leveraging statistics from the revision control history.

Read more...Formal-Based Design and Verification of SoC Arbitration Protocols: A Comparative Analysis of TDMA and Round-Robin

As System-On-Chips (SoCs) Are increasing in size and complexity, their validation and verification have become important and more difficult to achieve. Currently, the most widely used SoC design is typically bus based and consists of shared communication resources managed by dedicated arbiters that are in charge of serializing access r...

Read more...Keynote Paper on "Probing Attacks on Integrated Circuits: Challenges and Research Opportunities "

As a type of invasive physical attacks, probing attacks are able to access and directly monitor security critical nets of an IC and extract sensitive information. In this paper, the authors summarize the state-of-the-art probing and anti-probing technologies and their challenges, and discuss the opportunities in the relevant research. ...

Read more...Tackling Test Challenges for Interposer-Based 2.5-D Integrated Circuits

2.5-D integrated circuit (IC) is a cost-efficient alternative to through-silicon-via (TSV)-based 3-D IC. In this paper, the authors give a comprehensive summary of the testing challenges of 2.5-D ICs and their existing solutions. They then present a test architecture using e-fuses for prebond interposer testing and a method to reduce p...

Read more...Perspective from Francky Catthoor and Guido Groeseneken "Will Chips of the Future Learn How to Feel Pain and Cure Themselves? "

Extended transistor scaling has brought us a lot of benefits, but also a myriad of problems, including severe reliability issues [1]. To extend the scaling path as far as possible, system architects and technologists have to work together. They have to find solutions—e.g., at system level—to realize self-healing chips, chips that can d...

Read more...Call for Contributions Special Issue on Architecture Advances Enabled by Emerging Technologies

Prospective authors are requested to submit new, unpublished manuscripts for inclusion in the upcoming event described in this call for papers.

Read more...Interview: "An Interview With Professor Chenming Hu, Father of 3D Transistors "

Yao-Wen Chang, IEEE Design and Test of Computers Interviews Editor, spoke with the Father of 3D Transistors Dr. Chenming Hu at National Taiwan University, on 22 September 2016.

Read more...Book Review- "Engineering Secure Internet of Things Systems "

For the past thirty years, we have all suffered from poor security on our PCs, the Internet, and the World Wide Web. This has happened despite there being a relatively small number of reasonably expensive machines to protect—no more than a few per household. Our bank accounts and reputations may be at risk today, but seldom our lives. ...

Read more...IEEE Rebooting Computing Week

Isaac Newton is reported to have said in 1676: “If I have seen further, it is by standing on the shoulders of giants.” IEEE offers you another such opportunity in 2017.

Read more...Test Technology TC Newsletter

TTTC News The TTTC website always lists the latest features and information for its visitors! To find out more, please visit the website at <uri>http://www.ieee-tttc.org/</uri&gt;.

Read more...Corrections

In the July/August 2017 issue of IEEE Design&Test, the editor’s notes on p. 26 and 34 were incorrectly used. The correct Editor’s Notes are as follows.

Read more...The Last Byte "To Verification Infinity and Beyond "

When I worked for AT&T over 20 years ago, we knew that, if we messed up, the results could get onto the front page of the New York Times. This was not hyperbole; someone made a tiny change to telephone switch software, the change was thought too small to be worth verifying, and due to some obscure interactions between telephone swi...

Read more...