# **12TH ACM/IEEE** EMBEDDED SYSTEMS **WEEK**

# 2016 ESWEEK PROGRAM OCTOBER 2-7, 2016 | PITTSBURGH, PA | USA

SPONSORING SOCIETIES:

SIGBED SiG

Workshops (cont.)

| General Chairs'<br>Welcome Message3 |

|-------------------------------------|

| General Information4                |

| ESWEEK 2016 Overview5               |

| Sponsors6                           |

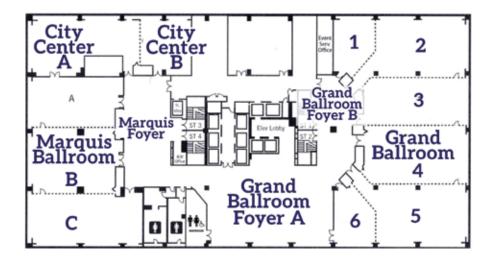

| Conference Venue Floorplan6         |

| Best Paper Candidates8              |

| Tutorials9                          |

| Monday ESWEEK Program15             |

| Tuesday ESWEEK Program22            |

| Wednesday ESWEEK Program29          |

| Workshops36                         |

| AC'16                               |

| CAIRES'16                           |

| CyPhy'1640                          |

| EWiLi'1642              |

|-------------------------|

| HILT'1643               |

| WESE'1645               |

| Symposia47              |

| RSP                     |

| ESTIMedia49             |

| Committees52            |

| ESWEEK Committees52     |

| CASES Committees        |

| CODES + ISSS Committees |

| EMSOFT Committees59     |

| IoT DAY Committees      |

# WELCOME TO ESWEEK 2016

Jörg Henkel | General Chair KIT Karlsruhe, Germany

Lothar Thiele | Vice-General Chair Swiss Federal Institute of Technology, Zurich, Switzerland

## Welcome to the IEEE/ACM Embedded Systems Week 2016!

This year the embedded systems community meets in Pittsburg, following the tradition of ESWEEK to rotate between Asia, Europe and North America.

At the core of ESWEEK from Monday to Wednesday are the three conferences CASES, Codes+ISSS and EMSOFT that received 63 technical papers (acceptance ratio 29%), 80 (26%) and 98 (26%), respectively. Besides the technical paper sessions, special sessions continue to be an important part of the conferences as experts give overviews of the newest embedded systems trends.

New this year is a focus on the Internet-of-Things: The "IoT Day" (part of Codes+ISSS) will take place on Tuesday presenting newest trends in IoT as a mix of technical papers, special sessions and invited speakers from an embedded systems point of view.

For the first time, the review process of the conferences was conducted in a journal-like two-stage peerreviewed process with the opportunity of minor/ major revision before final decision. This was in an effort to further increase the high quality of ESWEEK publications. It was also an intermediate step before ESWEEK intends to move to a journal-integrated publication model in 2017 where the majority of ESWEEK papers will be published either at an ACM or IEEE journal in an alternating way year by year.

Highlights of ESWEEK are the three keynotes: The Monday keynote by Prof. Srini Devadas from MIT will emphasize the importance of security in the age of the Internet-of-Things in "Secure Hardware Platforms for the Internet of Things (IoT)". The Tuesday keynote by Louis K. Scheffer from the Howard Hughes Medical Institute presents new paradigms of how to design software and hardware in "Learning from Life". Finally, the Wednesday keynote by Kaushik Roy from Purdue University presents the newest trends in approximate computing, a new paradigm that promises to increase the computing efficiency. His talk is entitled "Approximate Computing for Energy-efficient Error-resilient Systems".

The conference program will be concluded with the traditional panel on Wednesday afternoon focusing this year on "Embedded Systems Challenges in the Era of Cyber-Physical Systems and Internet of Things". It will provide the opportunity to discuss CPS and IoT topics with international experts. Further highlights are the five tutorials on Sunday covering safety, security, healthcare, on-chip learning and reactive programming.

The last two days of ESWEEK (Thursday and Friday) are dedicated to in-depth symposia and workshops covering topics like embedded multi-media, rapid system prototyping, approximate computing, industryacademia collaboration, CPS modeling, embedded OS, model-based development and embedded systems education.

Novel this year is the web page: It has undergone a new design and received additional content (for example an archive of previous ESWEEK events, a list of past best paper recipients etc.) and above all, it is now easy and convenient to browse from mobiles.

We want to thank all who made ESWEEK 2016 possible: The ESWEEK Organizing Committee, the ESWEEK Steering Committee, the Workshop and Symposia Organizers, MPA, the sponsors and all authors and speakers and attendees. Our special thanks go to Alex K. Jones the Local Arrangements Chair from the University of Pittsburg and his team for hosting ESWEEK 2016.

Have an inspiring, interesting and communicative ESWEEK 2016!

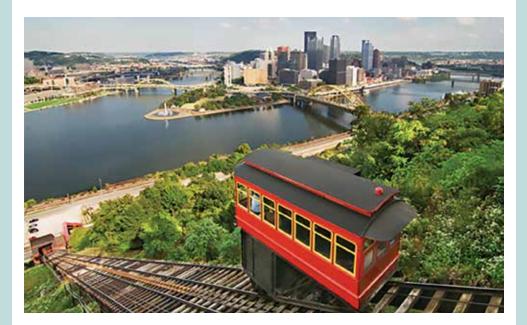

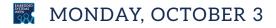

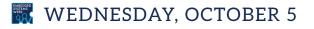

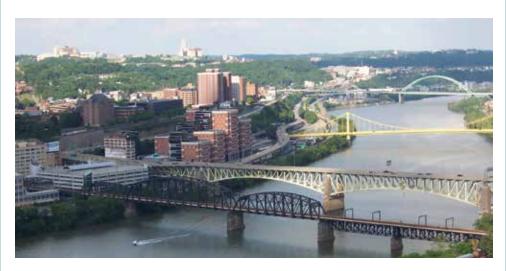

## Welcome to Pittsburgh

ESWEEK 2016 will take place in Pittsburgh, Pennsylvania, USA.

Known colloquially as the "City of Bridges", Pittsburgh is home to more bridges than even Venice! With worldclass sports, nature, culture, and now the leading conference on Embedded Systems, you're sure to find plenty to do in this great city. Pittsburgh is a city in western Pennsylvania at the junction of 3 rivers. Its Gilded Age sites, including the Carnegie Museum of Natural History, the Carnegie Museum of Art and the Phipps Conservatory and Botanical Gardens, speak to its history as an early-20th-century industrial capital. In the North Shore neighborhood are the modern Andy Warhol Museum, Heinz Field football stadium and PNC Park baseball stadium.

## **Conference Registration Fees**

Conference registration allows attendance to any of the three ESWEEK conferences, CODES+ISSS, CASES, and EMSOFT. Conference registration includes lunch on conference days, online conference proceedings, the Sunday Welcome Reception, and one ticket to the banquet. Student Conference registration does not include a banquet ticket, but one can be purchased. Workshops, Tutorials, and Symposia can be added on to your registration for an additional fee.

| Conference Member             | \$850 |

|-------------------------------|-------|

| Conference Non-Member         | \$975 |

| Conference Student Member     | \$500 |

| Conference Student Non-Member | \$650 |

| Thursday Workshop             | \$300 |

| Thursday & Friday Workshops   | \$360 |

| Tutorial Only Full Day        | \$150 |

| Tutorial Only Half Day        | \$75  |

| Symposia Member               | \$375 |

| Symposia Non-Member           | \$440 |

# ESWEEK 2016 OVERVIEW

## Sunday, October 2

Tutorials Cocktail Reception

## Monday, October 3

**Opening Session**

Keynote by Srini Devadas

CASES, CODES+ISSS, & EMSOFT Sessions

Poster Sessions

Technical Program Committee Dinner

## Tuesday, October 4

Keynote by Louis K. Scheffer

CASES, CODES+ISSS, EMSOFT & IoT Day Sessions

Poster Sessions

National Aviary - Social Event

## Wednesday, October 5

Keynote by Kaushik Roy

CASES, CODES+ISSS, EMSOFT & IoT Day Sessions

Poster Sessions

Best Paper Awards Ceremony

ESWEEK Panel

## Thursday, October 6

AC'16 Workshop CAIRES'16 Workshop CyPhy'16 Workshop EWiLi'16 Workshop HILT'16 Workshop WESE'16 Workshop RSP Symposium ESTIMedia Symposium

## Friday, October 7

HILT'16 Workshop RSP Symposium ESTIMedia Symposium

## **Conference Venue Floorplan**

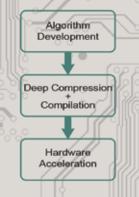

Thank You to Our Platinum Sponsors

**DeePhi** Tech focuses on deep learning, pushing the frontier of AI applications. Supported and invested by GSR Venture and Banyan Capital, we successfully developed a complete automation flow of compression, compiling and acceleration which achieves joint optimization between algorithm, software and hardware. A smaller, faster and more efficient deep learning processing unit (DPU) is released to public.

DeePhi has built deep collaboration with leading companies in fields of drone, security surveillance and cloud service. The FPGA based DPU platform achieves an order of magnitude higher energy efficiency over GPU on image recognition and speech detection. Deephi believes a joint optimization between algorithm, software and hardware would be the trend of deep learning. Innovation and high quality research is our driving force to grow, quick iteration between products and customers makes us grow fast.

## Technologies

DISCO

Algorithm, software, and hardware co-design, make deployment of deep learning algorithms simple, efficient and more accurate.

Team members of DeePhi Tech have worked on deep learning acceleration for years. Previous work were published at top machine learning and computer architecture conferences including NIPS, ICLR, FPGA, and ISCA. The technology of DeePhi is admitted by the industry and have been presented at Hot Chips 2016 together with Intel, ARM, Samsung, and other giants.

## Products

Deep Learning

## **Aristotle Archtecture**

Platform for CNN Supports all networks Supports object detection

## **Descartes Archtecture**

Platform for RNN/LSTM Supports speech recognition

DeePhi "Swift" DPU Platform

## CASES

## 3.2 LOCUS: LOW-POWER CUSTOMIZABLE MANY-CORE ARCHITECTURE FOR WEARABLES

### Authors:

Cheng Tan - National Univ. of Singapore Aditi Kulkarni - National Univ. of Singapore Vanchinathan Venkataramani - National Univ. of Singapore Manupa Karunaratne - National Univ. of Singapore Tulika Mitra - National Univ. of Singapore

Li-Shiuan Peh - *MIT*

## 3.3 D-PUF: AN INTRINSICALLY RECONFIGURABLE DRAM PUF FOR DEVICE AUTHENTICATION IN EMBEDDED SYSTEMS

### Authors:

Soubhagya Sutar - *Purdue Univ.* Arnab Raha - *Purdue Univ.* Vijay Raghunathan - *Purdue Univ.*

## 4.2 CAFFEPRESSO: AN OPTIMIZED LIBRARY FOR DEEP LEARNING ON EMBEDDED ACCELERATOR-BASED PLATFORMS

#### Authors:

Gopalakrishna Hegde - NTU Singapore Siddhartha - Nanyang Technological Univ. Nachiappan Ramasamy - NTU Singapore Nachiket Kapre - Nanyang Technological Univ.

## CODES + ISSS

## 2.1 A DESIGN TO REDUCE WRITE AMPLIFICATION IN OBJECT-BASED NAND FLASH DEVICES

#### Authors:

Jie Guo - Univ. of Pittsburgh Chuhan Min - Univ. of Pittsburgh Tao Cai - Jiangsu Univ. Yiran Chen - Univ. of Pittsburgh

## 3.1 FAST AND CYCLE-ACCURATE SIMULATION OF MULTI-THREADED APPLICATIONS ON SMP ARCHITECTURES USING HYBRID PROTOTYPING

#### Authors:

Ehsan Saboori - Concordia Univ. Samar Abdi - Concordia Univ.

## 4.1 FAULT INJECTION AT HOST-COMPILED LEVEL WITH STATIC FAULT SET REDUCTION FOR SOC FIRMWARE ROBUSTNESS TESTING

## Authors:

Petra R. Maier - Technische Univ. München Veit Kleeberger - Infineon Technologies Daniel Mueller-Gritschneder - Technische Univ. München Ulf Schlichtmann - TU München

## EMSOFT

## 3.1 LOCALLY OPTIMAL REACH SET OVER-APPROXIMATION FOR NONLINEAR SYSTEMS

### Authors:

Chuchu Fan - Univ. of Illinois at Urbana Champaign James Kapinski - Toyota Technical Center Xiaoqing Jin - Toyota Technical Center Sayan Mitra - Univ. of Illinois at Urbana Champaign

## 3.2 UNDERMINER: A FRAMEWORK FOR AUTOMATICALLY IDENTIFYING NON-CONVERGENT BEHAVIORS IN BLACK BOX SYSTEM MODELS

## Authors:

Ayca Balkan - Univ. of California, Los Angeles Paulo Tabuada - Univ. of California, Los Angeles Jyotirmoy Deshmukh - Toyota Technical Center Xiaoqing Jin - Toyota Technical Center James Kapinski - Toyota Technical Center

## 6.1 REAL-TIME CACHE MANAGEMENT FOR MULTI-CORE VIRTUALIZATION

#### Authors:

Hyoseung Kim - *Carnegie Mellon Univ.* Raj Rajkumar - *Carnegie Mellon Univ.*

## SUNDAY, OCTOBER 2 TUTORIALS SCHEDULE

|                  | Marquis A                                              | Marquis B                                               | Marquis C                                                                                                                               |  |

|------------------|--------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| 8:00 -<br>12:00  | AADL for Secure &<br>Safe Systems Design &<br>Analysis | IoT Security and<br>Privacy Challenges<br>and Solutions | When Embedded<br>Systems meet Life<br>Sciences: Microfluidic<br>Biochips for Real-Time<br>Healthcare                                    |  |

| 10:15 -<br>10:30 | Coffee Break   Room: Foyer                             |                                                         |                                                                                                                                         |  |

| 13:00 -<br>14:00 | Algorithms and<br>Hardware for Learning<br>On-a-Chip   | IoT Security and<br>Privacy Challenges<br>and Solutions | Next-Generation<br>Embedded Systems:<br>Functional Reactive<br>Programming, Formal<br>Verification, and Real-<br>Time Virtual Resources |  |

| 14:00 -<br>14:15 | Coffee Break   Room: Foyer                             |                                                         |                                                                                                                                         |  |

| 14:15 -<br>17:00 | Algorithms and<br>Hardware for Learning<br>On-a-Chip   | IoT Security and<br>Privacy Challenges<br>and Solutions | Next-Generation<br>Embedded Systems:<br>Functional Reactive<br>Programming, Formal<br>Verification, and Real-<br>Time Virtual Resources |  |

| 19:00 -<br>22:00 | Cocktail Reception   Room                              | City Center AB                                          |                                                                                                                                         |  |

## Tutorial 1 - AADL for Secure & Safe Systems Design & Analysis Time: 8:00 - 12:00 | Room: Marquis A

This tutorial presents the Architecture Analysis & Design Language (AADL) for architecture modeling and demon-strates how to use the Open Source AADL Tool Environment (OSATE) to design and analyze architecture models and check their security and safety requirements. Attendees will design architecture models, annotate them with safety and security information, and use OSATE's built-in analysis tools to analyze system latency, safety, and security.

This interactive tutorial will encourage hands-on participation. Attendees can bring their laptops, use the OSATE modeling tool suite to follow the tutorial instructions, and learn how to design and analyze architecture models. We will provide instructions before the tutorial for installing the modeling tool so that attendees will be ready to use it.

#### Biography:

Julien Delange is a senior member of the technical staff at the Carnegie Mellon Software Engineering Institute (SEI) in Pittsburgh, PA. He has been an active member of and contributor to the SAE AS-2C AADL standardization committee for more than 8 years. Julien has authored several research articles on architecture design and analysis, is a technical lead of the OSATE AADL modeling platform, and actively contributes to the Ocarina AADL code generator.

Before joining the SEI, Julien was a software engineer at the European Space Agency and worked on several research projects to design, analyze, and auto-produce safety-critical systems from models. He has a strong background in safety-critical systems and authored POK, the rst open-source ARINC-653-compliant micro-kernel. He has a master's degree in computer science and embedded systems from University Pierre and Marie Curie in Paris and a doctorate in computer science from TELECOM-ParisTech in Paris, France.

#### Speaker:

Julien Delange - Carnegie Mellon Univ.

## Tutorial 2 - When Embedded Systems meet Life Sciences: Microfluidic Biochips for Real-Time Healthcare

Time: 8:00 - 12:00 | Room: Marquis C

## Organizers:

Mirela Alistar - Hasso-Plattner Institute Krishnendu Chakrabarty - Duke Univ. Jan Madsen - Technical Univ. of Denmark Tsung-Yi Ho - National Tsing Hua Univ. Robert Wille - Johannes Kepler Univ. of Linz

This tutorial will provide the participants with first-hand experience on the emerging technology of digital microfluidic biochips. In addition to an introductory theory session, this tutorial offers a unique (and firstever) hands-on lab, where the participants will directly interact with biochips.

First, the participants will be introduced to the envisioned use of biochips in synthetic biology and health care. Then, the participants will learn the technical challenges behind biochips, mainly the fluidic movement using electrowetting on dielectric and various fabrication techniques. Next, the tutorial will present an overview of the CAD tools for biochips focusing on their reliability in the presence of faults.

Afterwards, during a hands-on lab, the participants will experience all the steps of the workflow: application design, application synthesis, data collection and result interpretation. The participants will design their own application and execute it on an actual biochip. The hands-on lab will also provide a practical guide on custom fabrication of biochips.

#### **Biographies:**

Mirela Alistar has been working since 2010 on developing tools for digital microfluidic biochips. As a complement to her academic track (publications, keynotes, etc), Mirela is supporting open access research and she has organized citizen-science events, where she disseminates to the public with the aim of involving them into creating more knowledge. She has been leading Biologigaragen (the biohacking space in Copenhagen) obtaining numerous governmental grants, and couching the local universities on opening internal hackerspace. In 2016, she founded Bioflux, a startup with the vision of producing a widely used lab-on-a chip that can revolutionize healthcare and laboratory research.

Krishnendu Chakrabarty is the William H. Younger Distinguished Professor in the Department of Electrical and Computer Engineering at Duke University. He is a recipient of many awards, including the Humboldt Research Award, the IEEE Trans. CAD Donald O. Pederson Best Paper award, 11 best paper awards at major conferences, and the IEEE Computer Society (CS) Technical Achievement Award. His current research is on design-for-testability of integrated circuits, microfluidic biochips, and cybermanufacturing. He is a Fellow of ACM, Fellow of IEEE, and Golden Core Member of the IEEE CS. Currently he serves as the Editor-in-Chief of IEEE Transactions on VLSI Systems.

Jan Madsen received his Ph.D. in Computer Science from Technical University of Denmark (DTU) in 1992. He is Full Professor in Computer-Based Systems at Department of Applied Mathematics and Computer Science at DTU. His research interests include design, modeling, analysis, optimization and construction of microelectronic, microfluidic and microbiological computing systems. He has published more than 150 peer-reviewed conference and journal papers. Since 2008 he has worked on Design Automation for microfluidic biochips, where he got a Best Paper Award at CASES 2009. Since 2011 he has coordinated research on synthetic biology with the vision to link it with biochip research.

Tsung-Yi Ho received his Ph.D. in Electrical Engineering from National Taiwan University in 2005. He is a Professor with the Department of Computer Science of National Tsing Hua University, Hsinchu, Taiwan. His research interests include design automation and test for microfluidic biochips and nanometer integrated circuits. He was a recipient of the Best Paper Awards at the VLSI Test Symposium (VTS) in 2013 and IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems in 2015.

Robert Wille received the Diploma and Dr.-Ing. degrees in computer science from the University of Bremen, Germany, in 2006 and 2009, respectively. Since 2015, he is full professor at the Johannes Kepler University Linz, Austria. His research interests include the development of design technologies for various application areas – with a particular focus on emerging technologies such as microfluidic biochips. This includes work in the domain of verification and proof engines as well as the synthesis and optimization. Since 2007, he published more than 130 journal and conference papers in this area and was repeatedly awarded.

## Tutorial 3 - Next-Generation Embedded Systems: Functional Reactive Programming, Formal Verification, and Real-Time Virtual Resources *Time: 13:00 - 17:00 | Room: Marquis C*

Sophisticated digital systems are increasingly used to control complex physical components ranging from traditional stand-alone systems to highlynetworked cyber-physical systems. Functional reactive programming (FRP) has several benefits over imperative programming for implementing embedded software, and can potentially transform the way we implement next-generation embedded systems. The first part of this tutorial introduces a framework for accurate response time analysis, scheduling, and verification of embedded controllers implemented as FRP programs.

Real-time resource partitioning divides hardware resources into temporal partitions and allocates these partitions as virtual resources to application tasks. Open embedded systems make it easy to add and remove software applications as well as to increase resource utilization and reduce implementation cost when compared to systems which physically assign distinct computing resources to run different applications. The second part of this tutorial describes ways to maintain the schedulability of real-time tasks as if they were scheduled on dedicated physical resources.

## **Biography:**

Albert M. K. Cheng is Professor and former interim Associate Chair of the Computer Science Department at the University of Houston. He received the B.A. with Highest Honors in Computer Science, graduating Phi Beta Kappa at age 19, the M.S. in Computer Science with a minor in Electrical Engineering at age 21, and the Ph.D. in Computer Science at age 25, all from The University of Texas at Austin, where he held a GTE Foundation Doctoral Fellowship. A recipient of numerous awards, Prof. Cheng has over 220 refereed publications and is author of the popular textbook entitled Real-Time Systems (Wiley).

## Speaker:

Albert M. K. Cheng - Univ. of Houston

## Tutorial 4 - Algorithms and Hardware for Learning On-a-Chip Time: 13:00 - 17:00 | Room: Marquis A

Machine learning algorithms have made enormous progress in recent years. However their complexity still challenges the state-of-the-art computing platforms, especially when the application of interest is tightly constrained by the requirements of low power, high throughput and small latency. There is a timely research need to map the latest learning algorithms to application-specific systems, in order to achieve orders of magnitude improvement in performance, energy efficiency and compactness.

The overarching goal of this tutorial is to explore the potential of on-chip learning, to reveal algorithm and design needs, and to promote novel intelligent applications. The tutorial is organized to introduce the fundamental learning theories, discuss numerical algorithms and their complexity in implementation, explore representative hardware platforms and their performances, and present emerging applications in this field.

The intended audience of the tutorial include hardware designers, system architects and tool developers from various application domains who are interested in on-chip learning.

## **Biographies:**

Yu (Kevin) Cao received the Ph.D. degree in electrical engineering from University of California, Berkeley, in 2002. He is currently a Professor in the School of ECEE at Arizona State University. He has published numerous articles and two books on nano-CMOS modeling and physical design. His research interests include physical modeling of nanoscale technologies, design solutions for variability and reliability, reliable integration of postsilicon technologies, and hardware design for on-chip learning.

Xin Li received the Ph.D. degree in Electrical & Computer Engineering from Carnegie Mellon University in 2005. He is currently an Associate Professor in the ECE Department at Carnegie Mellon. His research interests include integrated circuit, signal processing and data analytics. Dr. Li was the Associate Editor of IEEE TBME, IEEE TCAD, ACM TODAES, IEEE D&T and JOLPE. He was the General Chair of ISVLSI and FAC. He received the NSF CAREER Award in 2012 and six Best Paper Awards from IEEE TCAD, DAC, ICCAD and ISIC.

#### Speakers:

Yu (Kevin) Cao - *Arizona State Univ.* Xin Li - *Carnegie Mellon Univ.*

## Tutorial 5 - IoT Security and Privacy Challenges and Solutions *Time: 8:00 - 17:00 | Room: Marquis B*

Gartner estimates that a total of 26 billion connected devices will exist by the year 2020, with the majority being IoT and wearable devices. Security of these devices then becomes a great concern. In this tutorial, we give an overview of the challenges and tasks device manufacturers face when developing new devices and introducing themselves to a new market. We then cover some common pitfalls that we have encountered in our study of IoT and wearable devices. We provide detailed examples of our experimentation with devices with emphasis on the Nest Thermostat, the Nike+ Fuelband, the Centron Ultron C1SR electric meter, and other popular IoT devices. Lastly we conclude by presenting solutions that have been proposed by both industry and academia.

Besides the introduction to the IoT security problem, hands-on labs are also prepared for all audience. Modern and commercial IoT devices will be provided where audiences can practice how the devices can be compromised, causing device malfunction as well as other consequences.

#### **Biographies:**

Yier Jin is an assistant professor of Computer Engineering at the University of Central Florida, an associate partner of the Intel Collective Research Institute for Secure Computing, and member of the Florida Institute of Cybersecurity. He holds a Ph.D. in Electrical Engineering from Yale University. His research has focused on developing methods for ensuring the security and trustworthiness of the integrated circuits and systems. He has contributed several key solutions in the areas of trusted hardware, IoT and CPS security, hardware IP/SoC Formal Verification, security enhanced processor architecture for cybersecurity, gate-level netlist reverse engineering, and emerging device design for hardware security.

Ahmad-Reza Sadeghi is a full professor of Computer Science at Technische Universität Darmstadt, Germany. He is the head of the System Security Lab at the Center for Advanced Security Research Darmstadt (CASED) and the Director of the Intel Collaborative Research Institute for Secure Computing (ICRI-SC) at TU-Darmstadt. He holds a Ph.D. in Computer Science from the University of Saarland in Saarbrücken, Germany. Prior to academia, he worked in Research and Development of Telecommunications enterprises, amongst others Ericsson Telecommunications.

Dean Sullivan<sup>\*</sup> and Orlando Arias<sup>\*</sup> (Hands-on Lab session student assistants)

#### Speakers:

Yier Jin - Univ. of Central Florida Ahmad-Reza Sadeghi - Technische Univ. Darmstadt

|                     | Marquis A                                                                                                                                                         | Marquis B                                                            | Marquis C                                                                                    |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| 8:15 (ct) -<br>9:00 | ESWEEK Opening Session   Room: Grand Ballroom                                                                                                                     |                                                                      |                                                                                              |  |  |

| 9:00 -<br>10:00     | Monday Keynote: Srini Devadas, Massachusetts Institute of Technology,<br>"Secure Hardware Platforms for the Internet of Things (IoT)"<br>Room: Grand Ballroom 1-3 |                                                                      |                                                                                              |  |  |

| 10:00 -<br>10:30    | Coffee Break   Room: Foyer                                                                                                                                        |                                                                      |                                                                                              |  |  |

| 10:30 -<br>12:00    | <b>CASES:</b> Accelerators and<br>High Level Synthesis                                                                                                            | <b>CODES+ISSS:</b> Modeling<br>and Simulation of<br>Embedded Systems | <b>EMSOFT:</b> Timing and<br>Energy-Aware Modeling<br>and Programming of<br>Embedded Systems |  |  |

| 12:00 -<br>12:30    | Poster Session   Room: Foy                                                                                                                                        | Poster Session   Room: Foyer                                         |                                                                                              |  |  |

| 12:30 -<br>14:00    | Lunch   Room: Grand Ballroom 4-6<br>F1/10 Autonomous Racing Demo   Room: Foyer                                                                                    |                                                                      |                                                                                              |  |  |

| 14:00 -<br>15:30    | <b>CASES:</b> Reliability and Fault Tolerance                                                                                                                     | Special Session:<br>CODES+ISSS: Time in<br>Cyber-Physical Systems    | <b>EMSOFT:</b> Providing QoS<br>for Distributed Real-Time<br>Systems                         |  |  |

| 15:30 -<br>16:00    | Poster Session   Room: Foyer                                                                                                                                      |                                                                      |                                                                                              |  |  |

| 16:00 -<br>17:30    | <b>CASES:</b> Application<br>Driven Architectures:<br>Security, Genetics and<br>Wearables                                                                         | <b>CODES+ISSS:</b> A Splash<br>of Flash                              | <b>EMSOFT:</b> Verification<br>and Synthesis of<br>Embedded Control<br>Systems               |  |  |

| 17:30 -<br>18:00    | <b>Poster Session</b>   Room: Foyer<br>F1/10 Autonomous Racing Tutorial   Room: Marquis Ballroom                                                                  |                                                                      |                                                                                              |  |  |

| 19:30               | Technical Program Committee Dinner   Carlton Restaurant                                                                                                           |                                                                      |                                                                                              |  |  |

Opening Session Time: 8:15(ct) - 9:00 | Room: Grand Ballroom

## Keynote: Secure Hardware Platforms for the Internet of Things (IoT)

Time: 9:00 - 10:00 | Room: Grand Ballroom 1-3

Keynote Speaker:

Srini Devadas - Massachusetts Institute of Technology

The Internet is expanding into the physical world, connecting billions of devices. In this Internet of Things, two contradictory trends are appearing. On the one hand, the cost of security breaches is increasing as we place more responsibilities on the devices that surround us. On the other hand, computing elements are becoming small, disseminated, unsupervised, and physically exposed. Unfortunately, existing computing systems do not address many new attacks, such as resource sharing and physical attacks, presenting a significant vulnerability in future embedded systems. Hardware to the rescue! This talk will describe how secure systems can be built from the ground up.

Physical Unclonable Functions (PUFs) are a tamper resistant way of establishing shared secrets with a physical device. They rely on the inevitable manufacturing variations between devices to produce private keys that can be used as a hardware root of trust in a secure processor. Architectural isolation can be used to secure computation on a remote secure processor with a private key where the privileged software is potentially malicious as recently shown by Intel's Software Guard Extensions (SGX). The Sanctum secure processor architecture offers the same promise as SGX, namely strong provable isolation of software modules running concurrently and sharing resources, but protects against an important class of additional software attacks that infer private information by exploiting resource sharing.

The Sanctum design and implementation is based on the RISC-V processor and is completely open source, allowing for independent analysis and formal verification of security properties. The goal of the Sanctum project is to move secure hardware up to the level of scrutiny afforded by open source secure software.

## **Biography:**

Srini Devadas is the Webster Professor of Electrical Engineering and Computer Science at the Massachusetts Institute of Technology (MIT) where he has been on the faculty since 1988. He served as Associate Head of the Department of Electrical Engineering and Computer Science, with responsibility for Computer Science, from 2005 to 2011. Devadas's research interests span Computer-Aided Design (CAD), computer security and computer architecture and he has received significant awards from each discipline including the Richard Newton technical impact award and the IEEE Computer Society Technical Achievement award. He is a Fellow of the ACM and IFFF. He is a MacVicar Faculty Fellow and an Everett Moore Baker teaching award recipient, considered MIT's two highest undergraduate teaching honors.

## Chair:

Jörg Henkel - Karlsruhe Institute of Technology

## **CASES:** Accelerators and High Level Synthesis

Time: 10:30 - 12:00 | Room: Marquis A

## Chair:

Aviral Shrivastava - Arizona State Univ.

1.1 ILP-BASED MODULO SCHEDULING FOR HIGH-LEVEL SYNTHESIS

Julian Oppermann, Andreas Koch - *TU* Darmstadt Melanie Reuter-Oppermann - Karlsruhe Institute of Technology Oliver Sinnen - Univ. of Auckland 1.2 ENABLING OPENVX SUPPORT IN MW-SCALE PARALLEL ACCELERATORS

> Giuseppe Tagliavini - Univ. of Bologna Germain Haugou - ETH Zurich Andrea Marongiu - Univ. of Bologna Luca Benini - Università di Bologna

1.3 HANDLING LARGE DATA SETS FOR HIGH-PERFORMANCE EMBEDDED APPLICATIONS IN HETEROGENEOUS SYSTEMS-ON-CHIP Paolo Mantovani, Emilio G. Cota, Christian Pilato, Giuseppe Di Guglielmo, Luca Carloni -*Columbia Univ.*

## CODES + ISSS: Modeling and Simulation of Embedded Systems

Time: 10:30 - 12:00 | Room: Marquis B

## Chair:

Daniel Müller-Gritschneder - Technische Univ. München

**Co-Chair:** Oliver Bringmann- *Tübingen Univ., Germany*

1.1 A PRACTICAL METHODOLOGY TO VALIDATE THE STATISTICAL BEHAVIOR OF BLOOM FILTERS

Venkateshwar Kottapalli, Sunil Khatri - *Texas* A&M Univ.

1.2 SCALABLE AND REALISTIC BENCHMARK SYNTHESIS FOR EFFICIENT NOC PERFORMANCE EVALUATION: A COMPLEX NETWORK ANALYSIS APPROACH Yuaphun Yuo Paul Bordan, Univ of Southerry

Yuankun Xue, Paul Bogdan - Univ. of Southern California 1.3 AN ACCURATE AND FLEXIBLE EARLY MEMORY SYSTEM POWER EVALUATION APPROACH USING A MICROCOMPONENT METHOD

> Chi-Kang Chen - Industrial Technology Research Institute Hsin-I Wu, Chi-Ting Hsiao, Ren-Song Tsay -National Tsing Hua Univ.

# EMSOFT: Timing and Energy-Aware Modeling and Programming of Embedded Systems

Time: 10:30 - 12:00 | Room: Marquis C

## Chair:

Rolf Ernst - Technische Univ. Braunschweig

- 1.1 INVITED EMBEDDED TUTORIAL: ENERGY CONSUMPTION IN EMBEDDED SYSTEMS: ABSTRACTIONS FOR SOFTWARE MODELS, PROGRAMMING LANGUAGES, AND VERIFICATION METHODS Florence Maraninchi - Verimag

- 1.2 ENERGY AND TIMING AWARE SYNCHRONOUS PROGRAMMING Jia Jie Wang, Partha S. Roop - Univ. of Auckland Alain Girault - INRIA Grenoble - Rhône-Alpes

- 1.3 FLEXIBLE SUPPORT FOR TIME AND COSTS IN SCENARIO-AWARE DATAFLOW Michael Bungert - Saarland Univ. Arnd Hartmanns - Univ. of Twente

Holger Hermanns - Saarland Univ.

## F1/10 Autonomous Racing Demo at ESWeek

## *Time: 12:30 | Room: Foyer*

The F1/10 competition focuses on creating a meaningful and challenging design experience for students. The competition involves designing, building, and testing an autonomous 1/10th scale F1 race car (capable of speeds in excess of 40MPH) all while learning about perception, planning, and control for autonomous navigation.

F1/10 team is creating the infrastructure necessary to allow anybody to build, drive, and race their own autonomous race car. From teams new to controls engineering, to seasoned controller designers, the content available on F1Tenth.org is engaging and informative for all audiences. Together, we are making autonomy accessible and exciting.

## **CASES: Reliability and Fault Tolerance**

Time: 14:00 - 15:30 | Room: Marquis A

## Chair:

Jingtong Hu - Oklahoma State Univ.

2.1 RUNTIME MANAGEMENT OF ADAPTIVE MPSOCS FOR GRACEFUL DEGRADATION Stavros Tzilis, Ioannis Sourdis - Chalmers Univ. of Technology Vasileios Vasilikos - Kenotom P.C. - I.K.E. Dimitrios Rodopoulos - IMEC Dimitrios Soudris - National Technical Univ. of Athens

## 2.2 TOWARDS THE DESIGN OF FAULT-TOLERANT MIXED-CRITICALITY SYSTEMS ON MULTICORES

Luyuan Zeng, Pengcheng Huang - ETH Zurich Lothar Thiele - Swiss Federal Institute of Technology Zurich

2.3 COMET: COMMUNICATION-OPTIMISED MULTI-THREADED ERROR-DETECTION TECHNIQUE

> Konstantina Mitropoulou, Vasileios Porpodas, Timothy M. Jones - Univ. of Cambridge

## Special Session: CODES + ISSS: Time in Cyber-Physical Systems Time: 14:00 - 15:30 | Room: Marquis B

#### Organizer:

Aviral Shrivastava - Arizona State Univ. Cyber-Physical systems are those that tightly integrate physical and computational systems. One of the big challenges in distributed cyber-physical systems is establishing a common notion of time between the physical world and the computational system. Many modern CPS, especially industrial automation systems, require the actions of different computational systems to be synchronized at much higher rates than is possible through adhoc designs. Fundamental research is needed in synchronizing clocks of computing systems to a higher degree, and even if the clocks are synchronized, designing CPS nodes so that they can perform actions in a synchronized manner is challenging. We need to find ways to specify distributed CPS applications, ways to specify and verify timing requirements on distributed CPS, confident top-down design methodologies that can ensure the system meets its timing requirements in the first go, dynamically creating and dissolving timing domains using differently build components, and much more.

Cyber Physical Systems are the next generation of more complex embedded systems. CPS are multidisciplinary in the sense that designing CPS requires the knowledge of mechanical, electrical, embedded systems, and control theory. While CODES+ISSS recognizes the importance of this challenge-domain, and welcomes and includes research papers in this direction, a top-down, vertical perspective of this active and important area of inquiry is often absent in the paper presentations. This special session comprises of speakers from industry, academia and government agencies, all coming in to give an overview of time-related challenges facing the industry and society. We will also go over the state-of-the-art and its limitations, what problems are somewhat solved, and where much more research is needed. Finally, we will present an overview of the CPS testbed that has been developed to test the timing of distributed CPS, and evaluate the effectiveness of timing-correct-by-construction methodologies.

### 1SS.1 TIMING IN CPS

Ya-Shian Li-Baboud - National Institute of Standards and Technology

### 1SS.2 TIME AND TIMELINESS

Kevin Stanton - Intel Corp.

**1SS.3 PROGRAMMING WITH TIME** Patricia Derler - National Instruments Corp.

### 1SS.4 TIMING TESTBED

Aviral Shrivastava - Arizona State Univ.

## EMSOFT: Providing QoS for Distributed Real-Time Systems

## Time: 14:00 - 15:30 | Room: Marquis C

## Chair:

Paul Bogdan - Univ. of Southern California

2.1 INVITED EMBEDDED TUTORIAL: LESSONS LEARNED ON ASSUMPTIONS AND SCALABILITY WITH TIME-AWARE INSTRUMENTATION

Sebastian Fischmeister, Guy Martin Tchamgoue - *Univ. of Waterloo*

## 2.2 MAKING DDS REALLY REAL-TIME WITH OPENFLOW

Hyon-Young Choi, Andrew King, Insup Lee -*Univ. of Pennsylvania*

## 2.3 EXPLORING THE PERFORMANCE OF ROS2 Yuya Maruyama - Osaka Univ. Shinpei Kato - The Univ. of Tokyo Takuya Azumi - Osaka Univ.

# CASES: Application Driven Architectures: Security, Genetics and Wearables

## Time: 16:00 - 17:30 | Room: Marquis A

#### Chair:

Oliver Bringmann - Univ. Tübingen

- 3.1 A REAL-TIME DIGITAL-MICROFLUIDIC PLATFORM FOR EPIGENETICS Mohamed Ibrahim, Craig Boswell, Krishnendu Chakrabarty, Kristin Scott, Miroslav Pajic -Duke Univ.

- 3.2 \* LOCUS: LOW-POWER CUSTOMIZABLE MANY-CORE ARCHITECTURE FOR WEARABLES

Cheng Tan, Aditi Kulkarni, Vanchinathan Venkataramani, Manupa Karunaratne, Tulika Mitra - *National Univ. of Singapore* Li-Shiuan Peh - *MIT*

## CODES + ISSS: A Splash of Flash

*Time: 16:00 - 17:30 | Room: Marquis B*

### Chair:

Lars Bauer - Karlsruhe Institute of Technology

#### Co-Chair:

Aviral Shrivastava - Arizona State Univ.

#### 2.1 \* A DESIGN TO REDUCE WRITE AMPLIFICATION IN OBJECT-BASED NAND FLASH DEVICES

Jie Guo, Chuhan Min - Univ. of Pittsburgh Tao Cai - Jiangsu Univ. Yiran Chen - Univ. of Pittsburgh 3.3 \* D-PUF: AN INTRINSICALLY RECONFIGURABLE DRAM PUF FOR DEVICE AUTHENTICATION IN EMBEDDED SYSTEMS

Soubhagya Sutar, Arnab Raha, Vijay Raghunathan - *Purdue Univ.*

2.2 HOW TO ENABLE SOFTWARE ISOLATION AND BOOST SYSTEM PERFORMANCE WITH SUB-BLOCK ERASE OVER 3D FLASH MEMORY

Hsin-Yu Chang, Chien-Chung Ho - National Taiwan Univ.

Yuan-Hao Chang - Academia Sinica Yu-Ming Chang - Macronix International Co. Ltd. Tei-Wei Kuo - Academia Sinica & National Taiwan Univ.

### 2.3 REALIZING ERASE-FREE SLC FLASH MEMORY WITH REWRITABLE PROGRAMMING DESIGN

Yu-Ming Chang, Yung-Chun Li, Ping-Hsien Lin, Hsiang-Pang Li - *Macronix International Co. Ltd.*

Yuan-Hao Chang - Academia Sinica

## EMSOFT: Verification and Synthesis of Embedded Control Systems Time: 16:00 - 17:30 | Room: Marguis C

### Chair:

Oleg Sokolsky - Univ. of Pennsylvania

## 3.1 \*LOCALLY OPTIMAL REACH SET OVER-APPROXIMATION FOR NONLINEAR SYSTEMS

Chuchu Fan - Univ. of Illinois at Urbana Champaign James Kapinski - Toyota Technical Center Xiaoqing Jin - Toyota Technical Center Sayan Mitra - Univ. of Illinois at Urbana Champaign

## 3.2 \*UNDERMINER: A FRAMEWORK FOR AUTOMATICALLY IDENTIFYING NON-CONVERGENT BEHAVIORS IN BLACK BOX SYSTEM MODELS

Ayca Balkan, Paulo Tabuada - Univ. of California, Los Angeles Jyotirmoy Deshmukh - Toyota Technical Center Xiaoqing Jin - Toyota Technical Center James Kapinski - Toyota Technical Center

3.3 ROBUST CONTROLLER SYNTHESIS OF SWITCHED SYSTEMS USING COUNTEREXAMPLE GUIDED FRAMEWORK Hadi Ravanbakhsh, Sriram Sankaranarayanan - Univ. of Colorado

## Tutorial: F1/10 Autonomous Racing

Time: 17:30 | Room: Marquis Ballroom

1/10th the scale. 10 times the fun! Autonomous Racing Competition | F1Tenth.org

## \*\*\*\*\* NO REGISTRATION FEES REQUIRED! \*\*\*\*\*

It is often said in racing that 'if everything seems under control then you're not going fast enough'.

In the F1/10 autonomous racing competition, teams use the same 1/10th scale platform to race against each other and test limits of their control.

The cars can reach racing speeds of up to 40mph!

In this tutorial you will learn about the principles of real-time perception, planning, and control for autonomous navigation. We will cover the hardware and software necessary to BUILD, DRIVE, and RACE a 1/10th scale F1 autonomous race car.

This is a very practical tutorial: all instruction is directly relevant to building and running the race car we have developed. The goal is to enable students and researchers with various backgrounds to start their own autonomous racing effort and jump-start an autonomous race competition!

More info at http://f1tenth.org/

## Organizers:

Madhur Behl and Rahul Mangharam University of Pennsylvania TUESDAY, OCTOBER 4 SCHEDULE OF EVENTS

EMBEDDED SYSTEMS WEEK

|                  | Marquis A                                                                                                                                                                                          | Marquis B                                                                                                                                    | Marquis C                                                                                                   | City Center AB                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8:15 -<br>9:00   | Breakfast   Room: Foyer                                                                                                                                                                            |                                                                                                                                              |                                                                                                             |                                                                                                                                                         |

| 9:00 -<br>10:00  | Tuesday Keynote: Louis K. Scheffer, Howard Hughes Medical Institute<br>"Learning from Life"   Room: Grand Ballroom 1-3                                                                             |                                                                                                                                              |                                                                                                             |                                                                                                                                                         |

| 10:00 -<br>10:30 | Coffee Break   Room: Foyer                                                                                                                                                                         |                                                                                                                                              |                                                                                                             |                                                                                                                                                         |

| 10:30 -<br>12:00 | <b>CASES:</b><br>Architectures for<br>Machine Learning                                                                                                                                             | <b>CODES+ISSS:</b><br>System-Level<br>Design                                                                                                 | <b>EMSOFT:</b><br>Verification of<br>Hybrid Systems                                                         | <b>IoT Day:</b> Internet<br>of Things:<br>Technologies<br>and Application<br>Challenges                                                                 |

| 12:00 -<br>12:30 | Poster Session   Room: Foyer                                                                                                                                                                       |                                                                                                                                              |                                                                                                             |                                                                                                                                                         |

| 12:30 -<br>14:00 | Lunch   Room: Grand Ballroom 4-6                                                                                                                                                                   |                                                                                                                                              |                                                                                                             |                                                                                                                                                         |

| 14:00 -<br>15:30 | Special Session:<br>CASES:<br>Power and<br>Thermal<br>Management<br>in Massive<br>Multicore Chips:<br>Theoretical<br>Foundation meets<br>Architectural<br>Innovation<br>and Resource<br>Allocation | Special Session:<br>CODES+ISSS:<br>Harnessing the<br>Power of Big<br>Data – Computing<br>Technology to<br>Transform Big<br>Data into Insight | <b>EMSOFT:</b><br>Efficient and<br>Adaptive Resource<br>Management<br>and Hardware<br>Abstraction           | <b>IoT Day:</b> Self-aware<br>Systems for the<br>Internet-of-Things                                                                                     |

| 15:30 -<br>16:00 | Poster Session   Roo                                                                                                                                                                               | om: Foyer                                                                                                                                    |                                                                                                             |                                                                                                                                                         |

| 16:00 -<br>17:30 | <b>CASES:</b> Binary<br>Code Analysis<br>and Debugging                                                                                                                                             | <b>CODES+ISSS:</b><br>Reliability and<br>Robustness                                                                                          | EMSOFT:<br>Timing Analysis<br>and Cache<br>Management with<br>Multi-Level Caches<br>in Real-Time<br>Systems | <b>IoT Day:</b> Making the<br>Internet-of-Things a<br>Reality: From Smart<br>Models, Sensing<br>and Actuation to<br>Energy-Efficient<br>Architectures 4 |

| 17:30 -<br>18:00 | Poster Session   Room: Foyer                                                                                                                                                                       |                                                                                                                                              |                                                                                                             |                                                                                                                                                         |

| 18:30 -<br>22:00 | National Aviary - Social Event                                                                                                                                                                     |                                                                                                                                              |                                                                                                             |                                                                                                                                                         |

## **Keynote: Learning from Life**

Time: 9:00 - 10:00 | Room: Grand Ballroom 1-3

Keynote Speaker:

Louis K. Scheffer - Howard Hughes Medical Institute

Despite a half century of concerted effort, our best hardware and software combined still struggles to perform tasks that living organisms do effortlessly. Examples include object recognition, generalizing from few examples, and orchestrating collective behavior. For these and similar problems, decades of applying more and more computer power have realized only limited gains, making it clear the root problem is our lack of understanding of how to approach these tasks. One obvious path to cracking these problems is to understand how the brain solves them, but until now, this has always been at least as difficult as improving existing algorithms.

However, modern tools are finally becoming equal to the task of researching the brain, while progress on improving existing techniques remains incremental. So perhaps the most productive approach towards significant improvements in our hardware and software is to understand how the brain works, then copy these capabilities into man-made systems. Along these lines, we look at a few examples of how software and hardware might evolve, based upon what we already know of the brain.

#### **Biography:**

Lou Scheffer was trained as a EE at Caltech and Stanford. He spent the next 30 years designing both integrated circuits, and the software tools used to design them, at Hewlett Packard and Cadence. In 2008, he switched fields, moving to studying the brain at the Howard Hughes Medical Institute. There his research interests include methods to derive the detailed structure of the brain, and using this information to try to figure out how it works. His outside interests include SETI (the search for extraterrestrial life), and science education. He is the author of the usual collection of papers, books, and patents.

## Chair:

Lothar Thiele - ETH Zurich

## **CASES:** Architectures for Machine Learning

Time: 10:30 - 12:00 | Room: Marquis A

## Chair:

Jörg Henkel - Karlsruhe Institute of Technology

4.1 HYBRID NETWORK-ON-CHIP ARCHITECTURES FOR ACCELERATING DEEP LEARNING KERNELS ON HETEROGENEOUS MANYCORE PLATFORMS

> Wonje Choi, Karthi Duraisamy - Washington State Univ. Ryan Kim - Carnegie Mellon Univ. Janardhan Rao Doppa, Partha Pande -Washington State Univ. Radu Marculescu, Diana Marculescu -Carnegie Mellon Univ.

## 4.2 \* CAFFEPRESSO: AN OPTIMIZED LIBRARY FOR DEEP LEARNING ON EMBEDDED ACCELERATOR-BASED PLATFORMS

Gopalakrishna Hegde - NTU Singapore Siddhartha - Nanyang Technological Univ. Nachiappan Ramasamy - NTU Singapore Nachiket Kapre - Nanyang Technological Univ.

## 4.3 MATRIX MULTIPLICATION BEYOND AUTO-TUNING: REWRITE-BASED GPU CODE GENERATION

Michel Steuwer, Toomas Remmelg, Christophe Dubach - *The Univ. of Edinburgh*

<sup>\*</sup> Denotes Best Paper Candidate

## IOT Day: Internet of Things: Technologies and Application Challenges Time: 10:30 - 12:00 | Room: City Center AB

### Chair:

Arif Merchant - Google Inc.

2SS.1 IOT TECHNOLOGIES FOR EMBEDDED COMPUTING: A SURVEY Farzad Samie, Lars Bauer, Jörg Henkel -

Karlsruhe Institute of Technology

## 2SS.2 DISTRIBUTED QOS MANAGEMENT FOR INTERNET OF THINGS UNDER RESOURCE CONSTRAINTS

Farzad Samie - Karlsruhe Institute of Technology Vasileios Tsoutsouras, Sotirios Xydis - National Technical Univ. of Athens, Lars Bauer - Karlsruhe Institute of Technology, Dimitrios Soudris - National Technical Univ. of Athens

Jörg Henkel - Karlsruhe Institute of Technology

## 2SS.3 EVOLVING AUTHENTICATION DESIGN CONSIDERATIONS FOR THE INTERNET OF BIOMETRIC THINGS (IOBT)

Nima Karimianbahnemiri, Paul Wortman, Fatemen Tehranipoor - *Univ. of Connecticut*

## CODES + ISSS: System-Level Design

Time: 10:30 - 12:00 | Room: Marquis B

#### Chair:

Hyunok Oh - Hanyang Univ.

## Co-Chair:

Paul Bogdan - Univ. of Southern California

3.1 \*FAST AND CYCLE-ACCURATE SIMULATION OF MULTI-THREADED APPLICATIONS ON SMP ARCHITECTURES USING HYBRID PROTOTYPING

Ehsan Saboori, Samar Abdi - Concordia Univ.

## 3.2 EFFICIENT DESIGN SPACE EXPLORATION BY KNOWLEDGE TRANSFER

Dandan Li, Senzhang Wang, Shuzhen Yao -Beihang Univ. Yu-Hang Liu - Chinese Academy of Sciences Yuanqi Cheng - Beihang Univ. Xian-He Sun - Illinois Institute of Technology

## 3.3 OPTIMAL FUNCTIONAL-UNIT ASSIGNMENT AND BUFFER PLACEMENT FOR PROBABILISTIC PIPELINES

Weiwen Jiang, Edwin Sha, Qingfeng Zhuge, Xianzhang Chen - *Chongqing Univ.*

## **EMSOFT: Verification of Hybrid Systems**

Time: 10:30 - 12:00 | Room: Marquis C

Chair:

Miroslav Pajic - Duke Univ.

4.1 AN ALGORITHMIC APPROACH TO GLOBAL ASYMPTOTIC STABILITY VERIFICATION OF HYBRID SYSTEMS

Miriam García Soto - *IMDEA Software Institute,* Pavithra Prabhakar - *Kansas State Univ.*

4.2 VERIFYING CYBER-PHYSICAL SYSTEMS BY COMBINING SOFTWARE MODEL CHECKING WITH HYBRID SYSTEMS REACHABILITY Stanley Bak - United States Air Force Research Lab

Sagar Chaki - Carnegie Mellon Univ.

## 4.3 DARBOUX-TYPE BARRIER CERTIFICATES FOR SAFETY VERIFICATION OF NONLINEAR HYBRID SYSTEMS

Xia Zeng - East China Normal Univ. Wang Lin - Wenzhou Univ. Zhengfeng Yang - East China Normal Univ. Xin Chen - Nanjing Univ. Lilei Wang - East China Normal Univ.

## Special Session: CASES: Power and Thermal Management in Massive Multicore Chips: Theoretical Foundation meets Architectural Innovation and Resource Allocation

Time: 14:00 - 15:30 | Room: Marquis A

## Organizer:

Paul Bogdan - Univ. of Southern California

The realization of the promise of massive-scale integration depends on solutions to the problems of escalating power consumption and subsequent reduced reliability. Continuing progress and integration levels in silicon technologies make possible complete end-user systems consisting of extremely high number of cores on a single chip targeting either embedded or high-performance computing. However, without new paradigms of energy- and thermally-efficient designs, producing information and communication systems capable of meeting the computing, storage and communication demands of the emerging applications will be unlikely. The broad topic of power and thermal management of massive multicore chips is actively being pursued by a number of researchers worldwide. from a variety of different perspectives, ranging from workload modeling to efficient on-chip network infrastructure to resource allocation.

Successful solutions will likely adopt and encompass elements from all or at least several levels of abstraction. In this special session, we will present the Power-Thermal-Performance (PTP) trade-offs of massive multicore processors by considering three inter-related but varying angles, viz. on-chip traffic modeling, novel Networks-on-Chip (NoC) architecture and resource allocation.

- 1SS.1 THEORETICAL FOUNDATIONS FOR WORKLOAD MODELING WITH IMPLICATIONS ON POWER OPTIMIZATION Paul Bogdan - Univ. of Southern California

- 1SS.2 PERFORMANCE AND POWER MANAGEMENT IN WIRELESS NOC-ENABLED MULTICORE CHIPS Partha Pande - Washington State Univ.

1SS.3 THERMAL-DRIVEN RESOURCE ALLOCATION AND APPLICATION MAPPING FOR COMPLEX MANY CORE SYSTEMS

Jörg Henkel - Karlsruhe Institute of Technology

## Special Session: CODES + ISSS: Harnessing the Power of Big Data - Computing Technology to Transform Big Data into Insight *Time: 14:00 - 16:00 | Room: Marquis B*

#### Organizers:

Houman Homayoun - George Mason Univ. Farinaz Koushanfar - Univ. of California at San Diego

Extracting useful knowledge from the massive volume of data generated by various sources is introducing a paradigm shift in the way people and organizations proceed and interact with each other. While several advances in branches of technology - data sensing, communication, computation, and storage promise enabling the new applications, the computational complexity and variety of big data applications challenges the state-of-the-art algorithms and computing platforms. General-purpose one-size fits all solutions are unlikely to handle the vast spectrum of applications and computing domain options. This special session explores the potential of automated optimization and mapping of machine learning algorithms and their design needs. We will discuss the real-world challenges and opportunities faced for performing novel massive data analytics while considering various constraints. Particular focus will be on end-to-end specialized solutions that tune the application and data analysis algorithms to the underlying architecture with the objective of meeting the performance and cost constraints.

#### 2SS.1 AN OVERVIEW OF MICRON'S AUTOMATA PROCESSOR

Ke Wang, Kevin Angstadt, Chunkun Bo, Nathan Brunelle, Elaheh Sadredini, Tommy Tracy II, Jack Wadden, Mircea Stan, Kevin Skadron - Univ. of Virginia

### 2SS.2 ENABLING THE HIGH LEVEL SYNTHESIS OF DATA ANALYTICS ACCELERATORS

Marco Minutoli - Pacific Northwest National Lab Vito Giovanni Castellana - Polytechnic Univ. of Milan

Antonino Tumeo - *Pacific Northwest National Lab* Marco Lattuada, Fabrizio Ferrandi - *Politecnico di Milano*

## 2SS.3 BIG DATA ANALYTICS ON HETEROGENEOUS ACCELERATOR ARCHITECTURES

Avesta Sasan - Broadcom Corp. Houman Homayoun, Katayoun Neshatpour -George Mason Univ.

## 2SS.4 GOING DEEPER THAN DEEP LEARNING FOR MASSIVE DATA ANALYTICS UNDER PHYSICAL CONSTRAINTS

Bita D. Rouhani - Univ. of California at San Diego Azalia Mirhoseini - Google, Inc. Farinaz Koushanfar - Univ. of California at San Diego

## Special Session: IoT Day: Self-aware Systems for the Internet-of-Things Time: 14:00 - 15:30 Room: City Center AB

## Organizer:

Rolf Ernst - Technische Univ. Braunschweig The IoT will host a large number of co-existing cyberphysical applications. Continuous change, application interference, environment dynamics and uncertainty lead to complex effects which must be controlled to give performance and application guarantees. Application and platform self-configuration and self-awareness are one paradigm to approach this challenge. They can leverage context knowledge to control platform and application functions and their interaction. They could play a dominant role in large scale cyber-physical systems and systems-ofsystems, simply because no person can oversee the whole system functionality and dynamics. IoT adds a new dimension because Internet based services will increasingly be used in such system functions. Autonomous vehicles accessing cloud services for efficiency and comfort as well as to reach the required level of safety and security are an example. Such vehicle platforms will communicate with a service infrastructure that must be reliable and highly responsive.

Automated continuous self-configuration of data storage might be a good basis for such services up to the point where the different self-x strategies might affect each other, in a positive or negative form. The session will have 3 talks, "Self-aware Computing and the Internet of (Adaptive) Things" by Henry Hoffmann, University of Chicago, "Controlling Concurrent Change - A self-aware infrastructure for continuous change and evolution in automotive systems" by Rolf Ernst, TU Braunschweig, and "A big data approach to optimizing storage" by Arif Merchant, Google Research.

#### 3SS.1 SELF-AWARE COMPUTING AND THE INTERNET OF (ADAPTIVE) THINGS Henry Hoffmann - Univ. of Chicago

3SS.2 CONTROLLING CONCURRENT CHANGE - A SELF-AWARE INFRASTRUCTURE FOR CONTINUOUS CHANGE AND EVOLUTION IN AUTOMOTIVE SYSTEMS

Rolf Ernst - Technische Univ. Braunschweig

## 3SS.3 A BIG DATA APPROACH TO OPTIMIZING STORAGE

Arif Merchant - Google, Inc.

# EMSOFT: Efficient and Adaptive Resource Management and Hardware Abstraction

## Time: 14:00 - 15:30 | Room: Marquis C

### Chair:

Alain Girault - Inria Grenoble - Rhône-Alpes

- 5.1 A FLATTENED HIERARCHICAL SCHEDULER FOR REAL-TIME VIRTUALIZATION Michael Drescher, Vincent Legout, Antonio Barbalace, Binoy Ravindran - Virginia Tech

- 5.2 RMC: AN INTEGRATED RUNTIME SYSTEM FOR ADAPTIVE MANY-CORE COMPUTING Jinsu Park, Eunbi Cho, Woongki Baek - UNIST

- 5.3 AUTOMATIC HAL GENERATION FOR EMBEDDED MULTIPROCESSOR SYSTEMS Merten Popp, Orlando Moreira, Wim Yedema, Menno Lindwer - Intel Corp.

## **CASES: Binary Code Analysis and Debugging**

Time: 16:00 - 17:30 | Room: Marquis A

## Chair:

Henri-Pierre Charles - CEA-LIST

5.1 SPECULATIVE DISASSEMBLY OF BINARY CODE

M. Ammar Ben Khadra, Dominik Stoffel, Wolfgang Kunz - *Univ. of Kaiserslautern*  5.2 A JUMP-TARGET IDENTIFICATION METHOD FOR MULTI-ARCHITECTURE STATIC BINARY TRANSLATION

> Alessandro Di Federico, Giovanni Agosta -Politecnico di Milano

5.3 ON-THE-FLY LOAD DATA VALUE TRACING IN MULTICORES

> Mounika Ponugoti, Amrish Tewar, Aleksandar Milenkovic - *The Univ. of Alabama in Huntsville*

## Special Session: IoT Day: Making the Internet-of-Things a Reality: From Smart Models, Sensing and Actuation to Energy-Efficient Architectures *Time: 16:00 - 17:30 | Room: City Center AB*

## Organizer:

Paul Bogdan - Univ. of Southern California Advances in the physical sciences and engineering enable the development of internet-of-things (IoT) to understand, interface / interact and engineer physical world (systems). However, the deployment of multitude of wireless sensors and agents spanning many application domains (e.g. environmental, healthcare, smart interconnected automobiles and trucks, smart buildings) leads not only to tremendous requirements for communicating massive amounts of multiscale heterogeneous data, but also raises a number of outstanding challenges: (1) How can we construct efficient machine learning algorithms to construct mathematical models of the sensed data to enable better analysis, prediction and control? (2) How to overcome the energy wall in the IoT architecture while considering the computation, communication and control perspectives in a unified way? (3) How to design a decentralized control while ensuring composability in the IoT?

(4) How can the closed-loop control be enforced and brought closer to the sensing location to avoid the data movement and communication costs? To address these outstanding challenges, out-of-the-box approaches need to be explored.

## 4SS.1 COMPACT YET ACCURATE MATHEMATICAL MODELING OF COMPLEX SYSTEMS

Paul Bogdan - Univ. of Southern California

## 4SS.2 DESIGN CONSIDERATIONS FOR ARCHITECTING ULTRA-LOW POWER IOT EDGE DEVICES

Vijay Raghunathan - Purdue Univ.

4SS.3 CLOSING THE LOOP: COMPOSABLE ARCHITECTURES FOR REAL-TIME CONTROL OVER WIRELESS NETWORKS

Miroslav Pajic - Duke Univ.

4SS.4 ENERGY-EFFICIENT MANYCORE ARCHITECTURES FOR IOT APPLICATIONS Partha Pratim Pande - Washington State Univ.

## **CODES + ISSS: Reliability and Robustness**

Time: 16:00 - 17:30 | Room: Marquis B

### Chair:

Roman Lysecky - Univ. of Arizona

## Co-Chair:

Yier Jin - Univ. of Central Florida

4.1 \*FAULT INJECTION AT HOST-COMPILED LEVEL WITH STATIC FAULT SET REDUCTION FOR SOC FIRMWARE ROBUSTNESS TESTING Petra R. Majer - Technische Univ. München

Veit Kleeberger - Infineon Technologies Daniel Mueller-Gritschneder - Technische Univ. München Ulf Schlichtmann - TU München

## 4.2 OPTIMIZING THE LOCATION OF ECC PROTECTION IN NETWORK-ON-CHIP

Junshi Wang - Univ. of Electronic Science and Technology of China Letian Huang - Univeristy of Electronic Science and Technology of China Qiang Li, Guangjun Li - Univ. of Electronic Science and Technology of China Axel Jantsch - TU Wien

## 4.3 A DISTURBANCE-AWARE SUB-BLOCK DESIGN TO IMPROVE RELIABILITY OF 3D MLC FLASH MEMORY

Hung-Sheng Chang - National Taiwan Univ. Yuan-Hao Chang - Academia Sinica Tei-Wei Kuo - Academia Sinica & National Taiwan Univ.

Yu-Ming Chang, Hsiang-Pang Li - *Macronix International Co. Ltd.*

# EMSOFT: Timing Analysis and Cache Management with Multi-Level Caches in Real-Time Systems

## Time: 16:00 - 17:30 | Room: Marquis C

#### Chair:

Marco Bekooij - Univ. of Twente + NXP Semiconductors

## 6.1 \*REAL-TIME CACHE MANAGEMENT FOR MULTI-CORE VIRTUALIZATION

Hyoseung Kim, Raj Rajkumar - *Carnegie Mellon Univ.*

6.2 CACHE-RELATED PREEMPTION DELAY ANALYSIS FOR MULTI-LEVEL INCLUSIVE CACHES

> Zhenkai Zhang, Xenofon Koutsoukos -Vanderbilt Univ.

|                  | Marquis A                                                                                                                                                         | Marquis B                                                                                                                                         | Marquis C                                                                                                                        | City Center AB                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 8:15 -<br>9:00   | Breakfast Room: Foyer                                                                                                                                             |                                                                                                                                                   |                                                                                                                                  |                                                                                          |

| 9:00 -<br>10:00  | Wednesday Keynote: Kaushik Roy, Purdue Univ.:"Approximate Computing for<br>Energy-efficient Error-resilient Systems"   Room: Grand Ballroom 1-3                   |                                                                                                                                                   |                                                                                                                                  |                                                                                          |

| 10:00 -<br>10:30 | Coffee Break                                                                                                                                                      |                                                                                                                                                   |                                                                                                                                  |                                                                                          |

| 10:30 -<br>12:00 | <b>CASES:</b> Memory<br>Management                                                                                                                                | <b>CODES+ISSS:</b><br>Hungry for Power:<br>Energy Efficiency<br>in Heterogeneous<br>Multiprocessors                                               | <b>EMSOFT:</b><br>Autonomous<br>Systems and their<br>Verification                                                                | <b>IoT Day:</b> Internet-<br>of-Things:<br>Key Enablers<br>and Assistive<br>Technologies |

| 12:00 -<br>12:30 | Poster Session   Room: Foyer                                                                                                                                      |                                                                                                                                                   |                                                                                                                                  |                                                                                          |

| 12:30 -<br>14:00 | Lunch   Room: Grand Ballroom 4-6                                                                                                                                  |                                                                                                                                                   |                                                                                                                                  |                                                                                          |

| 14:00 -<br>15:30 | Special Session:<br>CASES:<br>Eastern Wisdom:<br>Neuromorphic<br>Computing<br>Research in China                                                                   | Special Session:<br>CODES+ISSS:<br>I am a Chip,<br>Therefore: Can<br>I Think? - The<br>Dawn of Self-<br>Awareness in<br>Cyber-Physical<br>Systems | <b>EMSOFT:</b> Formal<br>Methods for<br>Robust and<br>Predictable<br>Embedded Systems                                            | <b>EMSOFT:</b><br>Techniques for<br>Real-Time Task and<br>Communication<br>Scheduling    |

| 15:30 -<br>16:00 | Poster Session Room: Foyer                                                                                                                                        |                                                                                                                                                   |                                                                                                                                  |                                                                                          |

| 16:00 -<br>17:30 | <b>CODES+ISSS:</b><br>Energy-Aware<br>Embedded<br>System<br>Architectures                                                                                         | <b>CODES+ISSS:</b><br>Acceleration<br>of Analytic<br>Workloads                                                                                    | EMSOFT:<br>Management of<br>Flash-Based and<br>Hybrid Memory<br>Systems for<br>Improved Latency,<br>Lifetime, and<br>Reliability |                                                                                          |

| 17:30 -<br>18:00 | Poster Session   Room: Foyer                                                                                                                                      |                                                                                                                                                   |                                                                                                                                  |                                                                                          |

| 18:00 -<br>19:30 | Best Paper Awards Ceremony & ESWEEK Panel: Embedded Systems Challenges in the<br>Era of Cyber-Physical Systems and Internet of Things<br>Room: Grand Ballroom 1-3 |                                                                                                                                                   |                                                                                                                                  |                                                                                          |

## 🕃 WEDNESDAY, OCTOBER 5

## Keynote: Approximate Computing for Energy-efficient Errorresilient Systems

Time: 9:00 - 10:00 | Room: Grand Ballroom 1-3

**Keynote Speaker:** Kaushik Roy - *Purdue Univ.*