# CONFERENCE PROGRAM

NOVEMBER 13-16, 2017 · Irvine, CA · ICCAD.COM

WIEEE S CAS CONTACTOR OF CONTACTOR SIGNATION OF CONTACTOR OF CONTACTOR

# • WELCOME TO THE 36<sup>TH</sup> ICCAD •

It is with great pleasure that I welcome you to the 36th International Conference on Computer Aided Design. ICCAD is being held for the first time in the city of Irvine, a place that I hold dear.

In this increasingly compute centric world, there is increased demand for electronic design automation with exciting changes and challenges being faced in the way we design, compute, and deploy systems. For over thirty-five years, ICCAD has been a premier forum that

has paved the way in creating systems which are fast, small, power efficient, low cost, correct, manufacturable, and reliable. Recent keynotes, papers, tutorials and workshops at ICCAD have addressed novel technologies, the exciting prospects offered by deep learning, newer memories, IoT, approximate computing, and security concerns amongst others. This year's program promises to be equally exciting. Executive committee members, the technical program committee members, volunteers and the staff from MP Associates have worked tirelessly over the last year to prepare a stimulating program.

The program consists of 29 regular paper sessions, with 105 papers drawn from a submission of 399 papers. For over a month, 125 technical program committee members scrutinized the papers, and in a face-to-face meeting selected these papers for inclusion in the program. There are nine special sessions and two embedded tutorials that will be presented during the three days. A record six workshops will be held on the Thursday after the regular conference. Three keynotes will be presented by eminent researchers. The first, on Monday, will be given by Krysta Svore from Microsoft Research titled "Quantum Computing: Revolutionizing computation through quantum mechanics". The Wednesday keynote will be by Todd Austin from The University of Michigan on "How EDA Could Save the World (of Computing)" and the CEDA Invited Keynote will be presented on Tuesday by Maja Matarić from the University of Southern California.

On Thursday, there are six stimulating workshops on a variety of trending topics. These are: Workshop on Hardware and Algorithms for Learning On-a-chip (HALO); International Workshop on Design Automation for Analog and Mixed-Signal Circuits; IEEE/ACM 10th Workshop on Variability Modeling and Characterization; Electronic Design Automation for Quantum Computers; EDA/CAD in the IoT eHealth Era: From Devices to Architectures, Applications, and Data Analytics; and, Workshop on Non-Conventional Approaches to Hard Optimization (NAHO). Note that these workshops have exciting programs in themselves with keynotes from leading exponents.

Once again ICCAD promises to be on the cutting edge of EDA research. We do hope you will be able to join us next year for ICCAD 2018 November 5 -9, Hilton San Diego Resort and Spa, San Diego, CA.

#### ICCAD 2017 GENERAL CHAIR

Sri Parameswaran Univ. of New South Wales School of Computer Science & Engineering

# • TABLE OF CONTENTS •

| Welcome Message 2                                           |

|-------------------------------------------------------------|

| General Information 4                                       |

| Best Paper Candidates & Committees 6                        |

| CADathlon at ICCAD 7                                        |

| Monday Schedule 8                                           |

| Opening Session & Award Presentations 10                    |

| Monday Keynote Address 11                                   |

| Monday Session Details 12                                   |

| ACM Student Research Competition Poster Session 16          |

| ACM Student Research Competition Technical Presentations 25 |

| Tuesday Schedule 26                                         |

| Tuesday Session Details 28                                  |

| Tuesday Invited Keynote Luncheon 36                         |

| ACM/SIGDA Membership Meeting 45                             |

| Wednesday Schedule 46                                       |

| Wednesday Keynote Address 48                                |

| Wednesday Session Details 49                                |

| Thursday Schedule 60                                        |

| Thursday Workshop Details 61                                |

| Executive Committee 67                                      |

| Technical Program Committee 68                              |

| Conference Sponsors 70                                      |

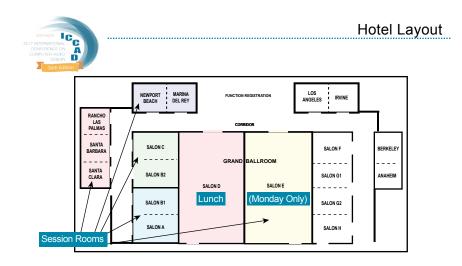

| Marriott Hotel Map 73                                       |

# **Registration Hours & Location**

#### Location: Salon E Foyer

Monday, November 137Tuesday, November 147Wednesday, November 157Thursday, November 167

7:00am - 6:00pm 7:30am - 6:00pm 7:30am - 6:00pm 7:00am - 4:00pm

# ICCAD 2017 Mobile App

Review the program, save sessions to your personalized conference schedule, read speakers abstracts, and connect with other attendees using the ICCAD 2017 mobile app provided by Whova, available for download today. Download Whova and search for **ICCAD 2017**.

# Proceedings

ICCAD Conference Papers will be delivered electronically online via a username and password. To access: http://proceedings.iccad.com Badge ID = Registration ID (on your badge) Your Email = Email address Please refer to your registration receipt to access the files you are eligible to view.

# • GENERAL INFORMATION •

# **Parking Information**

Discounted event self-parking of \$12.00 per vehicle.

# For Speakers & Presenters

## **SPEAKERS' BREAKFAST**

Please attend the day of your presentation!

| Location: Salon D      |               |

|------------------------|---------------|

| Monday, November 13    | 8:00 - 8:45am |

| Tuesday, November 14   | 7:15 - 8:00am |

| Wednesday, November 15 | 8:00 - 8:45am |

## **NEED PRACTICE?**

An AV Practice Room will be available in Suite 206, set up with a computer, LCD projector, and screen for you to practice/view your slides before your session.

#### Location: Suite 206

| Monday, November 13    | 7:00am - 6:00pm |

|------------------------|-----------------|

| Tuesday, November 14   | 7:00am - 6:00pm |

| Wednesday, November 15 | 7:00am - 6:00pm |

# ICCAD Social Media

Connect with ICCAD through Twitter @ICCAD. ICCAD will be tweeting hourly updates and conference highlights

# Stay Connected during the Conference

ICCAD 2017 is offering internet access in the meeting rooms for attendees. The Wi-Fi connection is Marriott Conference, password: ICCAD2017.

# Conference Management

Our mission is to facilitate networking, education and marketing with efficiency and precision in order to maximize customer experiences, and client profitability and recognition. We accomplish this by having a committed staff of trade show production

organizers with the training, technology tools, processes and experience to offer the best service in the industry. Visit **mpassociates.com** for more information.

# • BEST PAPER CANDIDATES & AWARD COMMITTEES •

# IEEE/ACM William J. McCalla ICCAD Best Paper Award Candidates

# **TUESDAY, NOVEMBER 14**

**4B.2** Speeding Up Crossbar Resistive Memory by Exploiting In-memory Data Patterns Wen Wen, Lei Zhao, Youtao Zhang, Jun Yang – Univ. of Pittsburgh

#### 5D.1 ATRIUM: Runtime Attestation Resilient Under Memory Attacks Shaza Zeitouni, Ghada Dessouky, Ahmad Ibrahim, Ahmad-Reza Sadeghi – Technische Univ. Darmstadt Orlando Arias – Univ. of Central Florida Dean Sullivan, Yier Jin – Univ. of Florida

6A.4 COMBA: A Comprehensive Model-Based Analysis Framework for High Level Synthesis of Real Applications

Jieru Zhao, Liang Feng, Wei Zhang – Hong Kong Univ. of Science and Technology Sharad Sinha – Nanyang Technological Univ.

Yun (Eric) Liang – Peking Univ.

Bingsheng He – National Univ. of Singapore

## WEDNESDAY, NOVEMBER 15

- **8A.3 SALT: Provably Good Routing Topology by a Novel Steiner Shallow-Light Tree Algorithm** Genjie Chen, Peishan Tu, Evangeline F.Y. Young – Chinese Univ. of Hong Kong

- 8C.1 Adaptive Error Recovery in MEDA Biochips Based on Droplet-Aliquot Operations and Predictive Analysis

Zhanwei Zhong, Zipeng Li, Krishnendu Chakrabarty - Duke Univ.

10B.1 Cost-Effective Design of Scalable High-Performance Systems using Active and Passive Interposers

Dylan Stow, Yuan Xie – Univ. of California, Santa Barbara Taniya Siddiqua, Gabriel H. Loh – Advanced Micro Devices, Inc.

# IEEE/ACM William J. McCalla ICCAD Best Paper Award Selection Committee

Naehyuck Chang (Chair) - Korea Advanced Institute of Science and Technology (KAIST) Deming Chen - Univ. of Illinois Urbana-Champaign Azadeh Davoodi - Univ. of Wisconsin - Madison Gang Qu - Univ. of Maryland, College Park Xuan Zeng - Fudan Univ., China

# Ten-Year Retrospective Most Influential Paper Award Selection Committee

Jason Cong (Chair) - Univ. of California, Los Angeles Duane Boning - Massachusetts Institute of Technology Vivek De - Intel Corp. Ramesh Karri - New York Univ. Tulika Mitra - National Univ. of Singapore

# • ACM SIGDA CADATHLON 2017 AT ICCAD •

# ACM SIGDA CADathlon 2017 at ICCAD

# Time: 8:00am - 5:00pm | Location: Salons A,B & C

The CADathlon is a challenging, all-day, programming competition focusing on practical problems at the forefront of Computer-Aided Design, and Electronic Design Automation in particular. The contest emphasizes the knowledge of algorithmic techniques for CAD applications, problem-solving and programming skills, as well as teamwork.

In its sixteenth year as the "Olympic games of EDA," the contest brings together the best and the brightest of the next generation of CAD professionals. It gives academia and the industry a unique perspective on challenging problems and rising stars, and it also helps attract top graduate students to the EDA field.

The contest is open to two-person teams of graduate students specializing in CAD and currently full-time enrolled in a Ph.D. granting institution in any country. Students are selected based on their academic backgrounds and their relevant EDA programming experiences. Travel grants are provided to qualifying students. The CADathlon competition consists of six problems in the following areas:

- (1) Circuit analysis

- (2) Physical design

- (3) Logic and behavioral synthesis

- (4) System design and analysis

- (5) Functional verification

- (6) Future technologies (Bio-EDA, Security, etc.)

More specific information about the problems and relevant research papers will be released on the Internet one week prior to the competition. The writers and judges that construct and review the problems are experts in EDA from both academia and industry. At the contest, students will be given the problem statements and example test data, but they will not have the judges' test data. Solutions will be judged on correctness and efficiency. Where appropriate, partial credit might be given. The team that earns the highest score is declared the winner. In addition to handsome trophies, the first and second place teams will receive cash award.

Contest winners will be announced at the ICCAD Opening Session on Monday morning and celebrated at the ACM/SIGDA Dinner and Member Meeting.

The CADathlon competition is sponsored by ACM/SIGDA and several Computer and EDA companies. For detailed contest information and sample problems from last year's competition, please visit the ACM/SIGDA website at http://www.sigda.org/programs/cadathlon.

#### ORGANIZING COMMITTEE:

Chair, Jingtong Hu, University of Pittsburgh, (jthu@pitt.edu) Vice Chair, Iris Hui-Ru Jiang, National Taiwan University (huiru.jiang@gmail.com) Vice Chair, JV Rajendran University of Texas at Dallas (jv.ee@utdallas.edu)

Sponsored by:

# • MONDAY SCHEDULE •

. . . . . . . . . . . . . .

#### 8:45 - 9:15am .... Opening Session & Awards

Location: Salon E

# 9:15 - 10:00am

# Keynote: Quantum Computing: Revolutionizing Computation Through Quantum Mechanics

Dr. Krysta Svore - Microsoft Research | Location: Salon E

## 10:00 - 10:30am

#### Coffee Break

Location: Salon E Foyer

#### **10:30***am* - **12:30***pm*..... Session 1A: Advanced Caching and In-Memory Processing

Location: Salon E

#### Session 1B: Camouflaging and Logic Encryption

Location: Salons A & B1

# Session 1C: Improving Manufacturability – From Design through Mask Generation

Location: Salons B2 & C

#### Special Session 1D: Cross-Layer Efforts for Combating Computationally Hard Problems

Location: Newport & Marina

#### **11:30am - 1:30pm** ..... ACM Student Research Competition Poster Session

Location: SSR

Sponsored by:

# • MONDAY SCHEDULE •

| 2:00 - 4:00pm<br>Session 2A: Modern Techniques for Challenging Verification Problems<br>Location: Salon E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Session 2B: Physical Attacks: Implementation, Simulation, and Synthesis<br>Location: Salons A & B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Special Session 2C: 3D Integration Beyond TSVs<br>Location: Salons B2 & C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Special Session 2D: AI for CPS: Machine Learning for Intelligent and Secure<br>Cyber-Physical Systems<br>Location: Newport & Marina                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4:00 - 4:30pm<br>Coffee Break<br>Location: Salon E Foyer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4:30 - 6:00pm<br>Session 3A: New Advances in Circuit Simulation<br>Location: Salon E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>Session 3B: Intelligent Control on Wheels<br/>Location: Salons A &amp; B1</li> <li>Session 3C: Next Generation System Level Design Methods<br/>Location: Salons B2 &amp; C</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Special Session 3D: 2017 CAD Contest<br>Location: Newport & Marina<br>Sponsored by:<br>SUICon to Software cādence (Contest Contest Cont |

| 6:00 - 6:20pm<br>EDA Megatrends: Enabling a Wide and Dynamic Range of Applications<br>Location: Salons B2 & C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6:20 - 6:50pm<br>Networking Reception<br>Location: Salon E Foyer Sponsored by: Cādence<br>ACADEMIC NETWORK CALENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6:30 - 8:00pm<br>ACM Student Research Competition Technical Presentations<br>Location: Salon E<br>Sponsored by:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# Opening Session, Awards, and Keynote Time: 8:45am - 10:00am | Location: Salon E

Kick off the conference with opening remarks from the ICCAD Executive Committee members and hear the highlights of the conference. The IEEE/ACM William J. McCalla ICCAD Best Paper award will be announced along with other award presentations from IEEE and ACM.

#### IEEE/ACM WILLIAM J. MCCALLA ICCAD BEST PAPER AWARD

This award is given in memory of William J. McCalla for his contributions to ICCAD and his CAD technical work throughout his career.

#### Front-End Award:

#### 6A.4 COMBA: A Comprehensive Model-Based Analysis Framework for High Level Synthesis of Real Applications

Jieru Zhao, Liang Feng, Wei Zhang – Hong Kong Univ. of Science and Technology Sharad Sinha – Nanyang Technological Univ. Bingsheng He – National Univ. of Singapore

#### Back-End Award:

#### 8A.3 SALT: Provably Good Routing Topology by a Novel Steiner Shallow-Light Tree Algorithm

Genjie Chen, Peishan Tu, Evangeline F.Y. Young – Chinese Univ. of Hong Kong

#### TEN YEAR RETROSPECTIVE MOST INFLUENTIAL PAPER AWARD

This award is being given to the paper judged to be the most influential on research and industrial practice in computer-aided design over the ten years since its original appearance at ICCAD.

#### 2008 Paper Titled: Lightweight Secure PUFs

Mehrdad Majzoobi, Farinaz Koushanfar - Rice Univ., Miodrag Potkonjak- Univ. of California, Los Angeles

ICCAD 2008, pp. 670 - 673

#### 2017 ACM/SIGDA PIONEER AWARD

Mary Jane Irwin, Emeritus Evan Pugh University Professor in Computer Science and Engineering - *Pennsylvania State University* For contributions to VLSI architectures, electronic design automation and community mentorship.

#### IEEE CEDA OUTSTANDING SERVICE AWARD

Dr. Frank Liu - IBM Research Austin For outstanding service to the EDA community as ICCAD General Chair in 2016.

#### IEEE CEDA ERNEST S. KUH EARLY CAREER AWARD

Ayse Coskun - Boston University

For sustained and outstanding contributions to energy-efficient system-level design, including temperature-aware design and management, 3D-stacked system design, and management of large-scale computing systems.

#### **ACM/SIGDA CADATHALON**

Introduction of the 2017 winners.

# • KEYNOTE ADDRESS •

# Keynote: Quantum Computing: Revolutionizing Computation Through Quantum Mechanics Time: 9:15am - 10:00am | Location: Salon E

#### Speaker:

#### Dr. Krysta Svore - Microsoft Research

In 1981, Richard Feynman proposed a device called a "quantum computer" to take advantage of the laws of quantum physics to achieve computational speed-ups over classical methods. Quantum computing promises to revolutionize how and what we compute. Over the course of three decades, quantum algorithms have been developed that offer fast solutions to problems in a variety of fields including number theory, optimization, chemistry, physics, and materials science. Quantum devices have also significantly advanced such that components of a scalable quantum computer have been demonstrated; the promise of implementing quantum algorithms is in our near future. I will attempt to explain some of the mysteries of this disruptive, revolutionary computational paradigm and how it will transform our digital age.

Biography: Dr. Krysta Svore is a Principal Researcher and Research Manager at Microsoft Research, where she leads the Quantum Architectures and Computation (QuArC) group. Dr. Svore joined Microsoft Research in 2006 and started the QuArC group in 2010. Her research focuses on the development and implementation of quantum algorithms, including the design of a scalable, fault-tolerant software architecture for translating a high-level quantum program into a low-level, device-specific quantum implementation. She has also developed techniques for protecting quantum computers from noise, including methods of quantum error correction, establishment of noise thresholds, and the development of improved decoders. She spent her early years at Microsoft developing machine-learning methods for web applications, including ranking, classification, and summarization algorithms. Her work in machine learning has expanded to include quantum algorithms for improve machine learning methods. Dr. Svore was recently appointed as a member of the Advanced Scientific Computing Advisory Committee of the Department of Energy and chaired the 2017 Quantum Information Processing Conference. Svore received an ACM Best of 2013 Notable Article award. In 2010, she was a member of the winning team of the Yahoo! Learning to Rank Challenge. Dr. Svore is honored as a Kavli Fellow of the National Academy of Sciences. She is a Senior Member of the Association for Computing Machinery (ACM), serves as a representative for the Academic Alliance of the National Center for Women and Information Technology (NCWIT), and is an active member of the American Physical Society (APS). Dr. Svore has authored over 65 papers and has filed over 20 patents. She received her PhD in computer science with highest distinction from Columbia University and her BA from Princeton University in Mathematics with a minor in Computer Science and French.

# Session 1A - Advanced Caching and In-Memory Processing

# Time: 10:30am - 12:30pm | Location: Salon E

#### Moderator:

Miroslav N. Velev - Aries Design Automation, LLC

This session presents four papers to advance the design of cache memories and take advantage of in-memory processing to accelerate applications. The first paper builds an efficient hybrid cache for multicore processors by exploiting value locality. The second paper explores cache bypassing and partitioning on GPUs. The third paper proposes a virtual persistent cache concept to remedy the long latency in Host-Aware Shingled Magnetic Recording (HA-SMR) drives. The final paper present a memristor-based in-memory processing for accelerating object recognition tasks.

- 1A.1 Leveraging Value Locality for Efficient Design of a Hybrid Cache in Multicore Processors Mohammad Arjomand - Georgia Institute of Technology

Amin Jadidi, Mahmut Kandemir, Chita Das - Pennsylvania State Univ.

- 1A.2 Exploring Cache Bypassing and Partitioning for MultiTasking on GPUs Yun (Eric) Liang, Xiuhong Li, Xiaolong Xie - Peking Univ.

- 1A.3 Virtual Persistent Cache: Remedy the Long Latency Behavior of Host-Aware Shingled Magnetic Recording Drives Ming-Chang Yang - Chinese Univ. of Hong Kong, Chinese Univ. of Hong Kong & Academia Sinica and National Taiwas Univ. Yuan-Hao Chang - Academia Sinica Fenggang Wu - Univ. of Minnesota, Twin Cities Tei-Wei Kuo - National Taiwan Univ. & Academia Sinica David H.C. Du - Univ. of Minnesota, Twin Cities

#### 1A.4 ORCHARD: Visual Object Recognition Accelerator Based on Approximate In-Memory Processing

Yeseong Kim, Mohsen Imani, Tajana Rosing - Univ. of California, San Diego

# Session 1B - Camouflaging and Logic Encryption Time: 10:30am - 12:30pm | Location: Salons A & B1

#### Moderator:

Fareena Saqib - Florida Institute of Technology

This session covers camouflaging and logic encryption attacks and countermeasures. Topics include attacks on decamouflaging sequential circuits without scan access, SAT-based attack on cyclic logic encryption, and a variety of novel countermeasure techniques for storing obfuscated master keys with quantifiable security and obfuscation of interconnects.

- 1B.1 Reverse Engineering Camouflaged Sequential Circuits Without Scan Access Mohamed El Massad, Siddharth Garg - New York Univ. Mahesh Tripunitara - Univ. of Waterloo

- 1B.2 Obfuscating the Interconnects: Low-Cost and Resilient Full-Chip Layout Camouflaging Satwik Patnaik - New York Univ. Mohammed Ashraf, Johann Knechtel, Ozgur Sinanoglu - New York Univ., Abu Dhabi

- 1B.3 CycSAT: SAT-Based Attack on Cyclic Logic Encryptions Hai Zhou, Ruifeng Jiang, Shuyu Kong - Northwestern Univ.

- **1B.4** Threshold-based Obfuscated Keys with Quantifiable Security Against Invasive Readout Shahrzad Keshavarz, Daniel Holcomb Univ. of Massachusetts, Amherst

# Session 1C - Improving Manufacturability -- From Design through Mask Generation Time: 10:30am - 12:30pm | Location: Salons B2 & C

#### Moderator:

Srikanth Venkataraman - Intel Corp.

Assuring manufacturability of present and future technologies and designs is crucial, and multiple methods are needed to achieve this. First, designs must better comprehend process constraints. The first paper effectively factors in implant-area constraints in multi-Vt designs, during mixed-cell-height place and route. Second, potential layout hotspots must be efficiently identified in a candidate design. The second paper achieves cluster count reduction during layout pattern classification using proposed heuristics. Third, manufacturable multi-patterned masks must be generated, and the third paper proposes a novel framework to simultaneously optimize layout decomposition and mask corrections. Finally, future technologies and designs will require joint multi-objective consideration of alternatives, as presented in the last paper.

1C.1 Mixed-Cell-Height Detailed Placement Considering Complex Minimum-Implant-Area Constraints Yen-Yi Wu, Yao-Wen Chang - National Taiwan Univ.

- **1C.2** Blockage-Aware Terminal Propagation for Placement Wirelength Minimization Sheng-Wei Yang, Yao-Wen Chang - National Taiwan Univ. Tung-Chieh Chen - Maxeda Technology, Inc.

- 1C.3 A Unified Framework for Simultaneous Layout Decomposition and Mask Optimization Yuzhe Ma - Chinese Univ. of Hong Kong Jhih-Rong Gao, Jian Kuang, Jin Miao - Cadence Design Systems, Inc. Bei Yu - Chinese Univ. of Hong Kong

1C.4 IR-drop Aware Design & Technology Co-Optimization for N5 Node with Different Device and Cell Height Options Luca Mattii - Technische Univ. Braunschweig & Cadence Design systems, Inc. Dragomir Milojevic, Peter Debacker, Yasser Sherazi - IMEC Mladen Berekovic - Technische Univ. Braunschweig Praveen Raghavan - IMEC

# Special Session 1D: Cross-Layer Efforts for Combating Computationally Hard Problems

## Time: 10:30am - 12:30pm | Location: Newport & Marina

#### Moderator:

Michael Niemier - Univ. of Notre Dame

#### Organizers:

X. Sharon Hu - Univ. of Notre Dame Michael Niemier - Univ. of Notre Dame

Computationally hard (i.e., NP-hard) problems are quintessential to many electronic design automation problems, and are also at the heart of many decision, scheduling, error-correction and security applications. Their NP-hard nature makes solving them extremely resource demanding, either in terms of computation time or hardware components or energy. Most of the efforts on improving solvers for such problems aim at developing more effective search algorithms with the understanding that these algorithms would eventually be implemented on modern general-purpose digital computing platforms such as multi-core or many-core processors or application specific digital circuits.

However, with Moore's Law coming to an end, exploring novel computational paradigms (e.g., quantum computing and neuromorphic computing) supported by emerging devices and alternative circuit styles is more imperative than ever. Recently there has been increased interest in cross-layer efforts for designing analog, or mixed-signal solvers for some specific NP-hard optimization problems based on continuous-time dynamical systems. Furthermore, a number of researchers are investigating approaches that exploit intrinsic properties exhibited by certain beyond-CMOS devices to solve NP-hard optimization problems.

In this special session, we highlight four cross-layer research efforts targeted at solving NP-hard problems (e.g., satisfiability, graph coloring, etc.) using computational primitives that (i) exploit spatio-temporal dynamics of coupled systems, and (ii) avoid Boolean abstraction in order to achieve high efficiencies with respect to energy and performance. The speakers will present a range of new solver implementations including mixed signal circuits based on conventional transistors, oscillators derived from phase transitions in correlated electron materials, and spin-based devices. While all approaches offer paths toward speedups and/or improvements in energy efficiencies of several orders of magnitude when compared to state-of-the-art approaches, challenges exist that the members of the EDA community are uniquely positioned to address, e.g., managing routing complexity as problem sizes scale, addressing noise tolerance, etc.

- 1D.1 Solving Constraint Satisfaction Problems: From Neural Dynamics to Silicon Chips Hesham Mostafa - Univ. of California, San Diego Giacomo Indiveri - Univ. of Zurich Lorenz K. Muller - ETH Zurich

- **1D.2** An Analog SAT Solver based on a Deterministic Dynamical System Xunzhao Yin, Zoltan Toroczkai, X. Sharon Hu - Univ. of Notre Dame

1D.3 Connecting Spectral Techniques for Graph Coloring and Eigen Properties of Coupled Dynamics: A Pathway for Solving Combinatorial Optimizations Abhinav Parihar - Georgia Institute of Technology Matthew Jerry, Nikhil Shukla, Suman Datta - Univ. of Notre Dame Arijit Raychowdhury - Georgia Institute of Technology

1D.4 Spin-Device Based Circuits for Computationally Hard Problems Kerem Y Camsari, Rafatul Faria, Brian M. Sutton, Supriyo Datta - Purdue Univ.

# ACM Student Research Competition Poster Session Time: 11:30am - 1:30pm | Location: SSR

Sponsored by Microsoft Research, the ACM Student Research Competition (SRC) is an internationally recognized venue enabling undergraduate and graduate students who are members of ACM and ACM SIGDA to:

- Experience the research world-for many undergraduates this is a first!

- Share research results and exchange ideas with other students, judges, and conference attendees.

- Rub shoulders with academic and industry luminaries.

- Understand the practical applications of their research.

- Perfect their communication skills.

- Receive prizes and gain recognition from ACM, and the greater computing community.

ACM SRC has three rounds:

- (1) abstract review

- (2) poster session (this session)

- (3) technical presentation

In the first round, 2-page research abstracts are evaluated by EDA experts from academia and industry to select participants for the second round (this session). For the ACM SRC at ICCAD 2016 competition, 20 participants were selected to present their research at ICCAD.

The posters are evaluated by EDA experts to select up to 5 participants in graduate and undergraduate categories to advance to the final round (technical presentation round). Students are expected to discuss their work with judges. Each judge will rate the student's visual presentation based on the criteria of uniqueness of the approach, the significance of the contribution, visual presentation, and quality of presentation.

More details can be found at: sigda.org/src

Sponsored by:

| cm | Association for<br>Computing Machinery |

|----|----------------------------------------|

|    | Advancina Computina as a Scient        |

# Lunch Time: 12:45pm - 1:45pm | Location: Salon D

Join fellow attendees for lunch in Salon D.

# Session 2A - Modern Techniques for Challenging Verification Problems

## Time: 2:00pm - 4:00pm | Location: Salon E

#### Moderator:

lan Harris - Univ. of California, Irvine

This session presents a range of SAT-based techniques to conquer major challenges in pre-silicon, post-silicon, repair and functional timing. The first paper proposes a novel approach for SAT-based model checking using approximations. The second paper introduces an approach for improving the coverage of electrical bugs in post silicon validation. The third paper formulates the problem of patching sequential circuits in the presence of retiming and resynthesis. The final paper in the session accelerates functional timing analysis by removing redundancies from the CNF formula that describes the functional and timing constraints on a path.

- 2A.1 Safety Model Checking with Complimentary Approximations Jianwen Li - Rice Univ. & East China Normal Univ.

Shufang Zhu, Yueling Zhang, Geguang Pu - East China Normal Univ.

Moshe Vardi - Rice Univ.

- 2A.2 An Automated SAT-Based Method for the Design of On-Chip Bit-Flip Detectors Pouya Taatizadeh, Nicola Nicolici - McMaster Univ.

- 2A.3 Sequential Engineering Change Order Under Retiming and Resynthesis Nian-Ze Lee - National Taiwan Univ. Victor Kravets - IBM Corp. Jie-Hong Roland Jiang - National Taiwan Univ.

- 2A.4 Accelerating Functional Timing Analysis with Encoding Duplication Removal and Redundant State Propagation Denny C.-Y. Wu, Pin-Ru Jhao, Charles H.-P. Wen - National Chiao Tung Univ.

#### MONDAY, NOVEMBER 13

# Session 2B - Physical Attacks: Implementation, Simulation, and Synthesis

## Time: 2:00pm - 4:00pm | Location: Salons A & B1

#### Moderator:

Sheldon Tan - Univ. of California, Riverside

Physical attacks on complex systems require ingenious attack implementations. Resilience against such attacks relies on efficient simulation, synthesis, and verification tools. This session starts with an efficient, high-resolution simulation method to automate electromagnetic side-channel leakage in cryptographic hardware. It also presents two papers on novel physical attacks: (1) fault injection attack on a deep neural network to disrupt the classification result and (2) a cache bank timing attack on AES to extract secret keys. Finally, the session introduces a new tool that adopts formal methods to synthesize circuitry for tracking timing flows.

- 2B.1 Efficient Simulation of EM Side-Channel Attack Resilience Amit Kumar, Cody Scarborough, Ali Yilmaz, Michael Orshansky - Univ. of Texas at Austin

- 2B.2 Fault Injection Attack on Deep Neural Network Yannan Liu, Lingxiao Wei, Bo Luo, Qiang Xu - Chinese Univ. of Hong Kong

- 2B.3 A Novel Cache Bank Timing Attack Zhen Hang Jiang, Yunsi Fei - Northeastern Univ.

- 2B.4 Clepsydra: Modeling Timing Flows in Hardware Designs Armaiti Ardeshiricham, Wei Hu, Ryan Kastner - Univ. of California, San Diego

# Special Session 2C: 3D Integration Beyond TSVs Time: 2:00pm - 4:00pm | Location: Salons B2 & C

#### Moderator:

Mark Yao - Boeing Corporation

#### Organizers:

Krishnendu Chakrabarty - Duke Univ. Sheldon Tan - UC Riverside Mehdi Tahoori - Karlsruhe Institute of Technology (KIT)

The continued down-scaling of nanoscale integrated circuits (IC) presents significant challenges with respect to manufacturability, reliability, cost, and power consumption. Recent work has therefore advanced the concept of "upscaling" through three-dimensional (3D) stacked ICs. Industry trends highlight the viability of 3D integration in actual products (e.g., the AMD Radeon R9 Fury X graphics card, Xilinx Virtex-7 2000T/H580T and Ultra-scale FPGAs). Flash memory vendors have announced multiple layers of memory in a single package, e.g., as many as 32 and 48 layers of Flash memory (Toshiba BiCS). Moore's law is now entering a new phase characterized by vertical integration ("3D Power Scaling" in the ITRS2.0 2015 report).

# Special Session 2C: 3D Integration Beyond TSVs (Cont.)

Today's 3D integration technology is primarily based on die/wafer stacking since it does not require major changes to the existing fabrication flow or retooling of fabrication processes. However, the increase in fabrication cost (foundries report that TSV processing adds 10% to the wafer cost), the keep-out-zone (KOZ) required for TSVs, and limitations on the die alignment precision impose limits on the device integration density that can be achieved using TSV-based 3D stacking. For example, it has been reported that a minimum KOZ of 3  $\mu$ m is required for ICs fabricated at the 20 nm technology node and the die alignment precision is imited to 0.5  $\mu$ m. Newer technologies for 3D integration are therefore being explored to exploit up-scaling to the fullest possible extent.

This special session will present a vision into the future of 3D integration. Speakers will address emerging directions in 3D integration techniques and challenges beyond traditional TSV-based 3D integration. Specific topics to be covered include monolithic 3D integration, long-term reliability assessment and design for reliability of interconnects in next-generation 3D ICs, wireless 3D interconnects, and on-chip silicon-photonics 3D interconnects. Each presentation will provide technology overview, describe design, test, and reliability challenges, and highlight recent advances.

Attendees will get holistic insights through lively presentations that will encapsulate the latest cutting-edge research in these emerging topics. This session will inform and inspire academic researchers as well as industry practitioners towards new innovations in these directions.

2C.1 Design Automation and Testing of Monolithic 3D ICs: Opportunities, Challenges, and Solutions

Kyungwook Chang - Georgia Institute of Technology

Abhishek Abhishek Koneru, Krishnendu Chakrabarty - Duke Univ.

Sung-Kyu Lim - Georgia Institute of Technology

2C.2 Leveraging Recovery Effect to Reduce Electromigration Degradation in Power/Ground TSV

Shengcheng Wang - Karlsruhe Institute of Technology

Zeyu Sun - Univ. of California, Riverside

Yuan Cheng - Shanghai Jiaotong Univ. Sheldon Tan - Univ. of California, Riverside Mehdi Tahoori - Karlsruhe Institute of Technology

- 2C.3 Energy-Efficient and Robust 3D NoCs with Contactless Vertical Links Srinivasan Gopal, Sourav Das, Partha Pratim Pande, Deuk Heo - Washington State Univ.

- 2C.4 Thermal-Sensitive Design and Power Optimization for a 3D Torus-Based Optical NoC Kang Yao, Yaoyao Ye Shanghai Jiao Tong Univ. Sudeep Pasricha - Colorado State Univ. Jiang Xu - Hong Kong Univ. of Science and Technology

# Special Session 2D: AI for CPS: Machine Learning for Intelligent and Secure Cyber-Physical Systems Time: 2:00pm - 4:00pm | Location: Newport & Marina

#### Moderator:

Deming Chen - Univ. of Illinois, Urbana-Champaign

#### Organizer:

Qi Zhu - Univ. of California, Riverside

With the proliferation of sensor data and advancement of processing power, machine learning techniques have shown great promise in cyber-physical systems (CPS) applications. These techniques are particularly effective for analyzing, controlling and optimizing complex CPS where the system dynamics and surrounding environment are hard to capture; however, applying them in practical systems often faces challenges from resource and timing constraints as well as reliability, predictability and security requirements. In this session, the four talks will introduce the application of machine learning techniques across a variety of CPS domains, including aerospace, agriculture, petroleum, and buildings and grid. They will demonstrate the effectiveness of using learning techniques, in particular those based on deep neural networks, to achieve artificial intelligence in CPS. They will discuss the encountered challenges in meeting system security, reliability and resource requirements, and present promising solutions.

2D.1 VoCaM: Visualization Oriented Convolutional Neural Network Acceleration on Mobile Systems Zhuwei Qin, Zirui Xu - George Mason Univ.

Yiran Chen - Duke Univ. Xiang Chen - George Mason Univ.

- 2D.2 An Autonomous Precision Irrigation Through Neural Reinforcement Learning Jiang Hu - Texas A&M Univ.

- 2D.3 Offshore Oil Spill Monitoring and Detection: Improving Risk Management for Offshore Petroleum Cyber-Physical Systems Xiaodao Chen, Dongmei Zhang, Lizhe Wang, Yuewei Wang - China Univ. of Geosciences

Albert Zomaya - The Univ. of Sydney Shiyan Hu - Michigan Technological Univ.

#### 2D.4 Deep Reinforcement Learning: Framework, Applications, and Embedded Implementations Hongjia Li - Syracuse Univ. Tianshu Wei - Univ. of California. Riverside

Ruizhe Cai - Syracuse Univ. of California, Riversi Ruizhe Cai - Syracuse Univ. Qi Zhu - Univ. of California, Riverside Yanzhi Wang - Syracuse Univ.

# Session 3A - New Advances in Circuit Simulation *Time: 4:30pm - 6:00pm | Location: Salon E*

#### Moderator:

Xin Li - Duke Univ.

With increased complexity of circuits and systems, efficient simulation continues to be critical yet challenging. The first paper describes an efficient methodology for sensitivity analysis of an eventdriven objective function. The second paper proposes a novel algorithm combining exponential integrators and Krylov subspace algorithms for nonlinear circuit simulation. The final paper develops a fast approach for electromigration analysis of multi-branch interconnect trees.

- 3A.1 DAGSENS: Directed Acyclic Graph Based Direct and Adjoint Transient Sensitivity Analysis for Event-Driven Objective Functions Karthik Aadithya, Eric Keiter, Ting Mei - Sandia National Laboratories

- 3A.2 Exploring the Exponential Integrators with Krylov Subspace Algorithms for Nonlinear Circuit Simulation

Xinyuan Wang - Univ. of California, San Diego

Hao Zhuang - ANSYS, Inc.

Chung-Kuan Cheng - Univ. of California, San Diego

- 3A.3 Fast Physics-based Electromigration Analysis for Multi-Branch Interconnect Trees Xiaoyi Wang, Yan Yan, Jian He - Beijing Advanced Innovation Center for Future Internet Technology & Beijing Univ. of Technology Sheldon X.-D. Tan, Chase Cook - Univ. of California, Riverside Shengqi Yang - Beijing Advanced Innovation Center for Future Internet Technology & Beijing Univ. of Technology

# Session 3B - Intelligent Control on Wheels Time: 4:30pm - 6:00pm | Location: Salons A & B1

#### Moderator:

Umit Ogras - Arizona State Univ.

This session focuses on intelligent control techniques to improve automotive performance parameters such as delay, path tracking, and battery capacity.

The first two papers integrate Model Predictive Control in automotive use-cases and demonstrate message delay prediction in Controller Area Network and dynamic model reconfiguration in finegrain and coarse-grain safety scenarios. The third paper presents an adaptive and cooperative quality-aware control for automotive cyber-physical systems.

- 3B.1 Online Message Delay Prediction for Model Predictive Control over Controller Area Network Amith Kaushal Rao, Haibo Zeng - Virginia Polytechnic Institute and State Univ.

- 3B.2 Hybrid State Machine Model for Fast Model Predictive Control: Application to Path Tracking Maral Amir, Tony Givargis - Univ. of California, Irvine

- 3B.3 ACQUA: Adaptive and Cooperative Quality-Aware Control for Automotive Cyber-Physical Systems Korosh Vatanparvar, Mohammad Abdullah Al Faruque - Univ. of California, Irvine

# Session 3C - Next Generation System Level Design Methods

## Time: 4:30pm - 6:00pm | Location: Salons B2 & C

#### Moderator:

Christopher Harris - Auburn Univ.

This session explores the application of emerging tools and techniques to challenges in system level computer design. We feature the adoption of machine learning techniques to hardware design space exploration, the use of hardware construction languages (HCLs) to promote design reuse for increasingly heterogeneous digital designs, and the automatic parallelization of applications for NoC-based multicore architectures.

- **3C.1** Cross-Program Design Space Exploration by Ensemble Transfer Learning Dandan Li, Shuzhen Yao - Beihang Univ. Senzhang Wang - Nanjing Univ. of Aeronautics and Astronautics Ying Wang - Chinese Academy of Sciences

- 3C.2 Hardware Reusability is FIRRTL Ground: Hardware Construction Languages, Compiler Frameworks, and Transformations Adam Izraelevitz, Jack Koenig, Patrick S. Li, Richard Lin, Angie Wang, Albert Magyar, Donggyu Kim, Colin Schmidt, Chick Markley, Jim Lawson, Jonathan Bachrach - Univ. of California, Berkeley

- 3C.3 A Load Balancing Inspired Optimization Framework for Exascale Multicore Systems: A Complex Networks Approach

Yao Xiao, Yuankun Xue, Shahin Nazarian, Paul Bogdan - Univ. of Southern California

# Special Session 3D: 2017 CAD Contest at ICCAD Time: 4:30pm - 6:00pm | Location: Newport & Marina

#### Moderator:

Myung-Chul Kim - IBM Corp.

#### Organizers:

Myung-Chul Kim - IBM Corp. Shih-Hsu Huang - Chung Yuan Christian Univ. Rung-Bin Lin - Yuan Ze Univ. Shigetoshi Nakatake - The Univ. of Kitakyushu

The CAD Contest at ICCAD is a challenging, multi-month R&D competition, focusing on modern and practical problems at the forefront of Electronic Design Automation (EDA). In its sixth year, the 2017 CAD Contest at ICCAD is among the premier worldwide academic programming contests, attracting 122 teams from 10 different regions/countries. This year, three contest problems in the areas of ECO logic synthesis, ECO routing and placement legalization for the advanced nodes are called for competition. This session gives an overview of the 2017 CAD Contest, presents the three contest problems and benchmarks, and announces the winners. It also provides a venue for the top-performing teams to showcase their key ideas via short video presentations. Based on the momentum accumulated by EDA contests, a talk on OpenDesign Flow Database 2.0 concludes the session by reporting recent progress towards building an academic infrastructure for VLSI design and EDA research.

3D.1 Overview of the 2017 CAD Contest at ICCAD Myung-Chul Kim - IBM Corp.

Shih-Hsu Huang - Chung Yuan Christian Univ.

Rung-Bin Lin - Yuan Ze Univ.

Shigetoshi Nakatake - Univ. of Kitakyushu

- **3D.2** ICCAD-2017 CAD Contest in Resource-Aware Patch Generation Ching-Yi Huang, Chih-Jen Hsu, Chi-An Wu - Cadence Taiwan, Inc. Kei-Yong Khoo - Cadence Design Systems, Inc.

- 3D.3 ICCAD-2017 CAD Contest in Net Open Location Finder with Obstacles Kai-Shun Hu, Ming-Jen Yang, Yu-Hui Huang, Bing-Yi Wong, Cindy Shen - Synopsys Taiwan Co., Ltd.

#### 3D.4 ICCAD-2017 CAD Contest in Multi-Deck Standard Cell Legalization and Benchmarks Nima Karimpour Darav - Microsemi Corporation Ismail Bustany - Mentor, A Siemens Business Andrew Kennings - Univ. of Waterloo

Ravi Mamidi - Mentor, A Siemens Business

3D.5 DATC RDF: Robust Design Flow Database

Jinwook Jung - Korea Advanced Inst. of Science and Technology Pei-Yu Lee, Yan-Shiun Wu - National Chiao Tung Univ. Nima Karimpour Darav - Microsemi Corporation Iris Hui-Ru Jiang - National Taiwan Univ. Victor N. Kravets - IBM T.J. Watson Research Center Laleh Behjat - Univ. of Calgary Yih-Lang Li - National Chiao Tung Univ. Gi-Joon Nam - IBM T.J. Watson Research Center

Sponsored by:

Additional Meeting: EDA Megatrends: Enabling a Wide and Dynamic Range of Applications Time: 6:00pm - 6:20pm | Location: Salons B2 & C

#### Speaker:

Alessandra Nardi - Cadence Design Systems, Inc.

Every industry follows trends, which are defined by the technological progress, society, culture. EDA industry is no exception here. However, EDA is a supplier to a much larger semiconductors industry serving itself a broad spectrum of applications, from consumer to automotive, from transistor to system-level. The challenge for EDA is to translate the markets needs into technology trends to be addressed or exploited to support the semiconductor industry and their customers. This presentation will have a brief overview of such challenges and opportunities and focus on few cases as example (e.g., enabling the fast

expanding, high demand automotive market).

Sponsored by:

# **Networking Reception** Time: 6:20pm - 6:50pm | Location: Salon E Foyer

Whatever your goal, networking receptions are the perfect venue for you to expand your network and keep you connected! Join us today to catch up with your colleagues and discuss the day's presentations with the conference presenters. All attendees are invited.

# Additional Meeting - ACM Student Research **Competition Technical Presentations** Time: 6:30pm - 8:00pm | Location: Salon E

The ACM Student Research Competition allows both graduate and undergraduate students to discuss their research with student peers, as well as academic and industry researchers, in an informal setting, while enabling them to attend ICCAD.

This session is the final round of ACM SRC at ICCAD 2017. Each student will present for 10 minutes, followed by a 5-minute guestion and answer period. This session will be attended by the evaluators and any interested conference attendees. The top three winners in each category will be chosen based on these presentations.

The undergraduate and graduate finalists will be eligible to compete in the ACM SRC Grand Finals to be held in June 2018. More details can be found at: sigda.org/src

Sponsored by:

SPONSORED BY

# • TUESDAY SCHEDULE •

# 8:00 - 10:00am

# Session 4A: Synthesis, Layout, and Crosspoint - Oh My!

Location: Salons A & B1

## Session 4B: System Designs with Emerging Memory Technologies Location: Salons B2 & C

# Session 4C: Towards Building Next Generation Embedded Software and Systems

Location: Newport & Marina

## Special Session 4D: Where Are the True Innovations and Potentials of IoT?

Location: SSR

# 10:00 - 10:30am

#### Coffee Break

Location: Salon E Foyer

# 10:30am - 12:00pm

## Session 5A: Split Manufacturing

Location: Salons A & B1

# Session 5B: Exploring Intricate Gate Level Optimization Trade-offs

Location: Salons B2 & C

## Session 5C: X-learning for IoT

Location: Newport & Marina

## Session 5D: New Directions in Secure Validation and Attestation

Location: SSR

# 12:00 - 12:30pm

Lunch Location: Salon D

# 12:30 - 1:30pm

CEDA Invited Keynote: Socially Assistive Robotics: Creating Robots that Care and Shaping the Future of Work

. . . . . . . . . . . . . .

Location: Salon D

# • TUESDAY SCHEDULE •

# 1:45 - 3:45pm

Session 6A: Novel Frameworks and Optimizations in Hardware Synthesis Location: Salons A & B1

Session 6B: New Advances in Approximate Computing and Neural Network Implementations

Location: Salons B2 & C

#### Session 6C: Power and Thermal Management for Cool Chips

Location: Newport & Marina

### Special Session 6D: FPGA CAD: Emerging Challenges and Solutions

Location: SSR

# 3:45 - 4:15pm

#### Coffee Break

Location: Salon E Foyer

## 4:15 - 6:15pm

## Session 7A: Taming Routability with Improved Placement

Location: Salons A & B1

### Session 7B: X Marks the Spot: Computing and Crossbars Location: Salons B2 & C

## Special Session 7C: Cross-layer Dependability of Medical CPS

Location: Newport & Marina

Special Session 7D: Automotive EDA: Constructing the Intersection of Silicon Valley and Motor City

Location: SSR

# 6:15 - 6:45pm

# Networking Reception

Location: Salon E Foyer

## 6:45 - 8:30pm

## ACM/SIGDA Member Meeting

Location: Salon D

# Session 4A - Synthesis, Layout, and Crosspoint – Oh My! Time: 8:00am - 10:00am | Location: Salons A & B1

#### Moderator:

Xiaoqing Xu - ARM, Inc.

Synthesis and layout sit at the core of electronic design automation (EDA). This session considers synthesis techniques for memristor-based logic and optical circuits, as well as layout decomposition using block copolymer materials. Crosspoint architectures for emerging spin-orbit torque magnetic memories are also discussed.

4A.1 SIMPLE MAGIC: Synthesis and In-Memory Mapping of Logic Execution for Memristor Aided Logic Rotem Ben Hur, Nimrod Wald, Nishil Talati, Shahar Kvatinsky - Technion - Israel Institute of Technology Dedicated Synthesis for MZI-Based Optical Circuits based on AND-Inverter Graphs 4A.2 Arighna Deb - KIIT Univ. Robert Wille - Johannes Kepler Univ. Linz Rolf Drechsler - Univ. of Bremen & DFKI GmbH 4A.3 Simultaneous Template Assignment and Layout Decomposition Using Multiple BCP Materials in DSA-MP Lithography Kuo-Hao Wu, Shao-Yun Fang - National Taiwan Univ. of Science and Technology 4A.4 PRESCOTT: Preset-based Cross-Point Architecture for Spin-Orbit-Torque Magnetic Random Access Memory Liang Chang, Zhaohao Wang - Beihang Univ. Alvin Oliver Glova - Univ. of California, Santa Barbara Jishen Zhao - Univ. of California, Santa Cruz Youguang Zhang - Beihang Univ.

All speakers are denoted in bold | \* denotes Best Paper Candidate

Yuan Xie - Univ. of California, Santa Barbara

Weisheng Zhao - Beihang Univ.

# Session 4B - System Designs with Emerging Memory Technologies

## Time: 8:00am - 10:00am | Location: Salons B2 & C

#### Moderator:

Wujie Wen - Florida International Univ.

This session will explore innovative system designs and applications with emerging memory technologies. Techniques are proposed to create better memory systems with Phase Change Memory and Resistive Memory. An approximate image storage is built with multi-level cell STT-MRAM. Asymmetric cryptography is performed efficiently with modular multipliers based on Racetrack memory.

- **4B.1** Cost-Effective Write Disturbance Mitigation Techniques for Advancing PCM Density Mohammad Khavari Tavana, David Kaeli Northeastern Univ.

- **4B.2\*** Speeding Up Crossbar Resistive Memory by Exploiting In-Memory Data Patterns Wen Wen, Lei Zhao, Youtao Zhang, Jun Yang - Univ. of Pittsburgh

- 4B.3 Approximate Image Storage with Multi-Level Cell STT-MRAM Main Memory Hengyu Zhao - Univ. of California, Santa Cruz Linuo Xue - Univ. of California, Santa Barbara Ping Chi - Intel Corp. Jishen Zhao - Univ. of California, Santa Cruz

- 4B.4 A Novel Two-Stage Modular Multiplier Based on Racetrack Memory for Asymmetric Cryptography Tao Luo - Nanyang Technological Univ. & Hong Kong Univ. of Science and Technology

Wei Zhang - Hong Kong Univ. of Science and Technology Bingsheng He - National Univ. of Singapore Douglas L. Maskell - Nanyang Technological Univ.

# Session 4C - Towards Building Next Generation Embedded Software and Systems

## Time: 8:00am - 10:00am | Location: Newport & Marina

#### Moderator:

Kapil Dev - Nvidia Corp.

This session explores the challenges involved in developing next generation embedded software and systems, which include mobile platforms, learning algorithms and applications like Advanced Driver Assist Systems and Autonomous Driving. The development of these systems demands new frameworks and methods for architecture exploration, modeling, and validation. Virtual Test bench, Distributed Learning algorithms, Reliable Computation and benchmarking automotive applications are the highlights of the approaches presented in this session.

#### 4C.1 VST: A Virtual Stress Testing Framework for Discovering Bugs in SSD Flash-Translation Layers Ren-Shuo Liu, Yun-Sheng Chang, Chih-Wen Hung - National Tsing Hua Univ.

4C.2 AdaLearner: An Adaptive Distributed Mobile Learning System for Neural Networks Jiachen Mao - Duke Univ.

Zhuwei Qin, Zirui Xu - George Mason Univ.

Kent W. Nixon - Duke Univ.

Xiang Chen - George Mason Univ.

Hai (Helen) Li, Yiran Chen - Duke Univ.

- 4C.3 NEMESIS: A Software Approach for Computing in Presence of Soft Errors Moslem Didehban, Aviral Shrivastava, Sai Ram Dheeraj Lokam - Arizona State Univ.

- 4C.4 An Open Benchmark Implementation for Multi-CPU Multi-GPU Pedestrian Detection in Automotive Systems

Matina Maria Trompouki - Univ. Politècnica de Catalunya **Leonidas Kosmidis** - Barcelona Supercomputing Center (BSC) Nacho Navarro - Barcelona Supercomputing Center (BSC) and Universitat Politècnica de Catalunya

# Special Session 4D - Where Are the True Innovations and Potentials of IoT?

## Time: 8:00am - 10:00am | Location: SSR

#### Moderator:

Deming Chen - Univ. of Illinois at Urbana-Champaign

#### Organizer:

Deming Chen - Univ. of Illinois at Urbana-Champaign

The rise of the Internet of Things (IoT) has led to an explosion of new sensor computing platforms, that dramatically expand the domains of applications, design complexity and diversity, and new and stringent design requirements over conventional embedded systems. In a wide variety of application domains, IoT device manufacturers must design and release new IoT devices regularly with shorter product cycles to maintain competitive advantages, differentiate products, sustain growth, and protect market share. Meanwhile, in order for IoT to realize its true potential, the whole eco-system needs to be built where IoT edge devices, communication channels, and data centers all demand new technology for delivering low-power/energy, low latency, high-throughput solutions in terms of sensing, communication, data analysis, and decision making. This special session will present four important themes in terms of IoT design and research from both industrial and academic experts to demonstrate the current state-of-the-art solutions and propose future compelling research directions. This special session is important to the audience of ICCAD when IoT, big data, and deep learning become important topics for the conference. The special session is very timely to share the current-state-of-the-art, and motivate and propose new research solutions to face the IoT revolution.

**4D.1** Novel Heterogeneous Computing Platforms and 5G Communications for IoT Applications Yuichi Nakamura, Hideyuki Shimonishi, Kozo Satoda, Dai Kanetomo, Yuki Kobayashi, Yasuhiko Matsunaga - *NEC Corp.*

#### 4D.2 Edge Segmentation: Empowering Mobile Telemedicine with Compressed Cellular Neural Networks

Xiaowei Xu, Qing Lu, Tianchen Wang, Jinglan Liu - Univ. of Notre Dame Cheng Zhuo - Zhejiang Univ. X. Sharon Hu, **Yiyu Shi** - Univ. of Notre Dame

#### 4D.3 CNN-based Pattern Recognition on Nonvolatile IoT Platform for Smart Ultraviolet Monitoring

Jinyang Li, Qingwei Guo, Fang Su, Zhe Yuan, Jinshan Yue - *Tsinghua Univ.* Jingtong Hu - *Univ. of Pittsburgh* Huazhong Yang, **Yongpan Liu** - *Tsinghua Univ.*

#### 4D.4 Machine Learning on FPGAs to Face the IoT Revolution

Anand Ramachandran, Di He - Inspirit IoT, Inc. Xiaofan Zhang, Chuanhao Zhuge, Wei Zuo - Univ. of Illinois at Urbana-Champaign Kyle Rupnow - Inspirit IoT, Inc. **Deming Chen** - Univ. of Illinois at Urbana-Champaign

# Session 5A - Split Manufacturing Time: 10:30am - 12:00pm | Location: Salons A & B1

#### Moderator:

Ujjwal Guin - Auburn Univ.

Split manufacturing defends against fab-based malicious activities caused by untrusted foundries. The first presentation describes how to address manufacturability alongside security. The second work considers scenarios where the back-end-of-line is untrusted. The final paper describes layout protection techniques to reduce the effect of proximity attacks.

#### 5A.1 Making Split Fabrication Synergistically Secure and Manufacturable