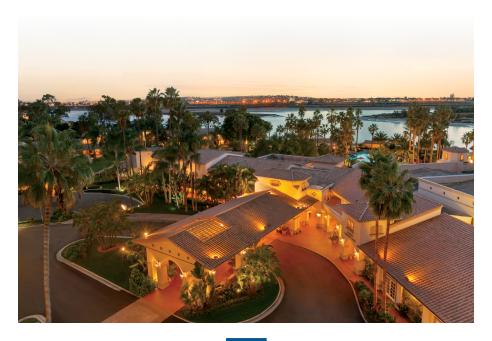

**NOVEMBER 5 - 8, 2018** Hilton San Diego Resort & Spa San Diego, CA **ICCAD.COM**

# WELCOME TO THE 37TH ICCAD

# FROM IRIS BAHAR ICCAD GENERAL CHAIR

Welcome to the 37th edition of the International Conference on Computer-Aided Design! For the first time, ICCAD is being held in San Diego. We are very excited to be testing out this new location. We hope you have a chance to get out and enjoy the city and the views as well as the ICCAD conference itself.

Jointly sponsored by IEEE and ACM, ICCAD is the premier forum to explore emerging technology challenges in electronic design automation, present leading-edge R&D solutions, and identify future roadmaps for design automation research areas. The members of the executive committee, the technical program committee, and numerous volunteers have spent the past several months preparing an exciting program for you!

This was another strong year for ICCAD in terms of number of regular paper submissions. Approximately 400 regular paper submissions were reviewed by our outstanding technical program committee. In the end, we have 98 papers spread over 26 sessions on diverse topics related to EDA that were selected during our technical program committee in a face-to-face meeting in June. We also had a record number of special session proposals submitted to ICCAD this year and decided to add an extra parallel track to our program on Tuesday to help accommodate the large number of high-quality special sessions and embedded tutorials. Altogether, we have 13 special sessions and 3 embedded tutorials on topics that complement the regular sessions.

We are delighted to host several distinguished keynote speakers: the Monday morning keynote on IoT and Cloud systems will be given by Professor Chandra Krintz from the University of California, Santa Barbara. On Tuesday, Andreas Olofsson from DARPA will present the IEEE CEDA Luncheon Distinguished Lecture on the agency's Electronics Resurgence Initiative. Finally, Dr. Rob Aitkens, ARM Fellow and Technology Lead at ARM Research, will present the Wednesday keynote on technology trends and their implications on EDA tools and flows. We hope you will find these keynotes interesting and informative.

We are also offering two special workshops on Sunday, before the conference officially begins. The first is an NSF-sponsored workshop on IoT systems. Then, on Sunday evening ICCAD will be hosting a Bias Busters workshop on implicit bias awareness and prevention. Both these events are free to all ICCAD registrants.

On Thursday, we have seven interesting workshops planned, on a variety of both new and established topics. Some of these workshops are long-time staples of ICCAD, while others are testing the waters for the first time. These workshops have exciting programs themselves, so we hope that many of you will take advantage of them and stay an extra day and San Diego.

Once again ICCAD promises to be an ultimate destination for those working on cutting edge EDA research. We do hope you will be able to join us in making this event a great and memorable one. Finally, we are grateful to our ICCAD 2018 sponsors and numerous supporters for making this year's conference another successful event. Enjoy ICCAD and San Diego!

# TABLE OF CONTENTS

| Welcome Message 2                                           |

|-------------------------------------------------------------|

| General Information                                         |

| CADathlon at ICCAD 6                                        |

| Sunday Workshops 7                                          |

| Best Paper Candidates & Committees 9                        |

| Monday Schedule 10                                          |

| Opening Session & Award Presentations 12                    |

| Monday Keynote Address 13                                   |

| Monday Session Details                                      |

| ACM Student Research Competition Poster Session 18          |

| ACM Student Research Competition Technical Presentations 27 |

| Tuesday Schedule 28                                         |

| Tuesday Session Details 30                                  |

| Tuesday Invited Keynote Luncheon 36                         |

| ACM/SIGDA Membership Meeting 45                             |

| Wednesday Schedule 46                                       |

| Wednesday Keynote Address 48                                |

| Wednesday Session Details 49                                |

| Thursday Schedule --------------------60                    |

| Thursday Workshop Details 61                                |

| Executive Committee 67                                      |

| Technical Program Committee 68                              |

| Conference Sponsors 70                                      |

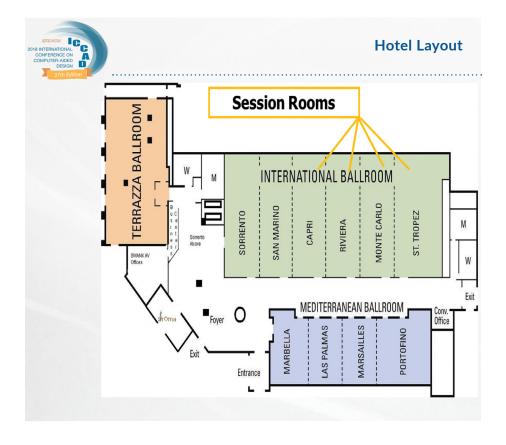

| Hilton Hotel Map 73                                         |

# GENERAL INFORMATION

# **Registration Hours & Location**

Location: Terrazza Foyer

Monday, November 5 7:00am - 6:00pm

Tuesday, November 6 7:30am - 6:00pm

Wednesday, November 7 7:30am - 6:00pm

Thursday, November 8 7:00am - 4:00pm

# ICCAD 2018 Mobile App

Review the program, save sessions to your personalized conference schedule, read speakers abstracts, and connect with other attendees using the ICCAD 2018 mobile app provided by Whova, available for download today. Download Whova and search for ICCAD 2018.

# **Proceedings**

ICCAD Conference Papers will be delivered electronically online via a username and password.

To access: http://proceedings.iccad.com Badge ID = Registration ID (on your badge)

Your Email = Email address

Please refer to your registration receipt to access the files you are eligible to view.

# GENERAL INFORMATION

# **Parking Information**

Discounted event self-parking of \$15.00 per vehicle per night.

Daytime rates \$5.00 up to three hours; \$8.00 for three - six hours; \$12 for six - twelve hours.

# For Speakers & Presenters

## SPEAKERS' BREAKFAST

Please attend the day of your presentation!

### Location: Terrazza Ballroom

Monday, November 5 7:30 - 8:15am Tuesday, November 6 7:30 - 8:15am Wednesday, November 7 7:30 - 8:15am

### **NEED PRACTICE?**

An AV Practice Room will be available in Private Dining Room (PDR), set up with a computer, LCD projector, and screen for you to practice/view your slides before your session.

### Location:

Monday, November 5 7:00 - 9:30am and 3:00 - 6:00pm

Tuesday, November 6 7:00 - 9:30am

Wednesday, November 7 7:00 -11:00am and 4:00 - 6:00pm

## **ICCAD Social Media**

Connect with ICCAD through Twitter @ICCAD. ICCAD will be tweeting hourly updates and conference highlights

# Stay Connected during the Conference

ICCAD 2018 is offering internet access in the meeting rooms for attendees.

The Wi-Fi connection is Hilton Resort, user name: iccad2018 password: iccad2018.

# Conference Management

Our mission is to facilitate networking, education and marketing with efficiency and precision in order to maximize customer experiences, and client profitability and recognition. We accomplish this by having a committed staff of trade show production organizers with the training, technology tools, processes and experience to offer the best

service in the industry.

Visit mpassociates.com for more information.

# ACM SIGDA CADATHLON 2018 AT ICCAD

## ACM SIGDA CADathlon 2018 at ICCAD

Sunday, November 4

Time: 8:00am - 5:00pm | Room: Terrazza Ballroom

In the spirit of the long-running ACM programming contest, the CADathlon is a challenging, all-day, programming competition focusing on practical problems at the forefront of Computer-Aided Design, and Electronic Design Automation in particular. The contest emphasizes the knowledge of algorithmic techniques for CAD applications, problem-solving and programming skills, as well as teamwork.

In its seventeenth year as the "Olympic games of EDA," the contest brings together the best and the brightest of the next generation of CAD professionals. It gives academia and the industry a unique perspective on challenging problems and rising stars, and it also helps attract top graduate students to the EDA field.

The contest is open to two-person teams of graduate students specializing in CAD and currently full-time enrolled in a Ph.D. granting institution in any country. Students are selected based on their academic backgrounds and their relevant EDA programming experiences. Travel grants are provided to qualifying students. The CADathlon competition consists of six problems in the following areas:

- (1) Circuit design and analysis

- (2) Physical design and design for manufacturability

- (3) Logic and high-level synthesis

- (4) System design and analysis

- (5) Verification and testing

- (6) Future technologies (Bio-EDA, Security, AI, etc.)

More specific information about the problems and relevant research papers will be released on the Internet one week prior to the competition. The writers and judges that construct and review the problems are experts in EDA from both academia and industry. At the contest, students will be given the problem statements and example test data, but they will not have the judges' test data. Solutions will be judged on correctness and efficiency. Where appropriate, partial credit might be given. The team that earns the highest score is declared the winner. In addition to handsome trophies, the first and second place teams will receive cash award.

Contest winners will be announced at the ICCAD Opening Session on Monday morning and celebrated at the ACM/SIGDA Dinner and Member Meeting.

The CADathlon competition is sponsored by ACM/SIGDA and several Computer and EDA companies. For detailed contest information and sample problems from last year's competition, please visit the ACM/SIGDA website at http://www.sigda.org/programs/cadathlon

For all inquiries, please send emails to: cadathlon@gmail.com

#### ORGANIZING COMMITTEE:

Chair, Iris Hui-Ru Jiang, National Taiwan University Vice Chair, Tsung-Wei Huang, University of Illinois Urbana-Champaign Vice Chair, Pei-Yu Lee, Maxeda Technology

# NSF Workshop on Internet-of-Things (IoT) Systems Time: 8:30am - 5:30pm | Room: Portofino

### Organizer:

Marilyn Wolf - Georgia Institute of Technology

Internet-of-Things systems are widely used in disciplines including manufacturing, logistics, and medicine. As IoT systems increase in scope and complexity, new challenges are presented. The workshop will explore emerging challenges and identify research opportunities with the goal of improving the capabilities and use case repertoire of IoT technology. Workshop participants will create a report on research challenges in IoT systems.

# Bias Buster Workshop @ ICCAD Time: 5:00 - 8:00pm | Room: Marseilles

### Speakers:

**Gerry Katilius** Google, Inc.

**Diana Marculescu** Carnegie Mellon Univ.

Unconscious (or implicit) bias is believed to be a significant factor that inhibits inclusivity and acts to stall or even thwart important efforts for increasing and celebrating diversity. Everyone has implicit or unconscious biases, and because they are unconscious, we are unaware of them. In this workshop, the first of its kind at ICCAD, the basis of implicit bias is presented and effective tools for increasing awareness and mitigation of its unwanted effects are provided. This important workshop is useful to every ICCAD participant—bystanders and advocates alike—who can intervene and effectively bust implicit bias when it occurs, either in themselves or in others. The workshop will present current understanding of what these biases are and how we can reduce their impacts in our behaviors and interactions with others. There will be role-playing activities to give attendees practice at identifying and responding to unconscious bias in day-to- day activities.

Background: Bias Busters @ Work (BB@Work) was created by Google as an extension of its Unconscious Bias @ Work Workshop (UB@Work), a course aimed at raising awareness of how unconscious biases work, how they can negatively influence workplace interactions, and what tools can help disrupt bias. In 2015, Google and Carnegie Mellon University created the Bias Busters @ University program, with Bias Busters@CMU being a version specifically tailored for Carnegie Mellon, first piloted by CMU's College of Engineering and School of Computer Science. More information on Bias Busters @ Work: https://rework.withgoogle.com/subjects/unbiasing

# BEST PAPER CANDIDATES

# IEEE/ACM William J. McCalla ICCAD Best Paper Award Candidates

### **MONDAY, NOVEMBER 5**

## 1A.2\* Analytical Solution of Poisson's Equation and Its Application to VLSI Global Placement

Wenxing Zhu- Fuzhou Univ. Zhipeng Huang- Fuzhou Univ. Jianli Chen - Fuzhou Univ. Yao-Wen Chang - National Taiwan Univ.

## **TUESDAY, NOVEMBER 6**

# 5C.1\* DNNBuilder: an Automated Tool for Building High-Performance DNN Hardware Accelerators for FPGAs

Xiaofan Zhang - Univ. of Illinois at Urbana-Champaign

Junsong Wang, - IBM Research - China Chao Zhu, - IBM Research - China Yonghua Lin, - IBM Research - China Jinjun Xiong - IBM T.J. Watson Research Center Wen-Mei Hwu - Univ. of Illinois at Urbana-Champaign Deming Chen - Univ. of Illinois at Urbana-Champaign

## WEDNESDAY, NOVEMBER 7

# 8A.2\* Parallelizable Bayesian Optimization for Analog and Mixed-Signal Rare Failure Detection with High Coverage

Hanbin Hu- Texas A&M Univ. Peng Li- Texas A&M Univ. Jianhua Z. Huang - Texas A&M Univ.

#### 9A.2\* GPU Acceleration of RSA is Vulnerable to Side-channel Timing Attacks

Chao Luo - Northeastern Univ. Yunsi Fei - Northeastern Univ. David Kaeli - Northeastern Univ.

### 9B.1\* SODA: Stencil with Optimized Dataflow Architecture

Yuze Chi - Univ. of California, Los Angeles Jason Cong - Univ. of California, Los Angeles Peng Wei - Univ. of California, Los Angeles Peipei Zhou - Univ. of California, Los Angeles

# 10B.1\* PolyCleaner: Clean your Polynomials before Backward Rewriting to Verify Million-gate Multipliers

Alireza Mahzoon - Universität Bremen Daniel Große - Universität Bremen / DFKI Rolf Drechsler - Universität Bremen / DFKI

# BEST PAPER AWARD COMMITTEES

# IEEE/ACM William J. McCalla ICCAD Best Paper Award Selection Committee

Joerg Henkel (Chair) - Karlsruhe Institute of Technology

Yier Jin - Univ. of Florida

**Youngsoo Shin** - Korea Advanced Institute of Science and Technology

Wei Zhang - Hongkong Univ. of Science and Technology Zheng Zhang - Univ. of California. Santa Barbra

Tulika Mitra - National Univ. of Singapore

## Ten-Year Retrospective Most Influential Paper Award Selection Committee

Naehyuck Chang (Chair) - Korea Advanced Institute of Science and Technology

**Ulf Schlichtmann** - Tech. Univ. of Munich **Thomas Wenisch** - Univ. of Michigan

**Evangeline Young** - Chinese Univ. of Hong Kong

Ramesh Karri - New York Univ.

Sung-Kyu Lim - Georgia Institute of Tech.

# TUTORIAL/SPECIAL SESSION COMMITTEE

**Yiran Chen** - Duke University

Shao-Yun Fang - National Taiwan Univ. Tim Güneysu - University of Bochum/DFKI Diana Marculescu - Carnegie Mellow Univ.

**Sherief Reda** - Brown Univ. **Robert Wille** - Univ. of Linz

# WORKSHOP SELECTION COMMITTEE

Naehyuck Chang - Korea Advanced Institute of Science and Technology Jörg Henkel - Karlsruhe Institute of Technology

# MONDAY SCHEDULE

8:30 - 9:00am .....

Opening Session & Awards

Location: Saint Tropez

9:00 - 10:00am

Adventures and Opportunities in Cyber-Physical Systems Research

Chandra Krintz - Univ. of California, Santa Barbara | Location: Saint Tropez

10:00 - 10:30am

Coffee Break

Location: Terrazza Foyer

10:30am - 12:30pm······

Session 1A: Analytical Techniques in Design Planning

Location: Saint Tropez

Session 1B: Ahoy! Anti-Piracy Techniques

Location: Monte Carlo

Session 1C: Flexibility Makes Learning Better

Location: Riveria

Special Session 1D: Emerging Reconfigurable Nanotechnologies: Can they Support Future Electronics?

Location: Capri

Location: Private Dining Room

Snonsored hv

12:45 - 1:45pm Lunch

Location: Bayside Terrace

# MONDAY SCHEDULE

1:45 - 3:45pm

Session 2A: It's Time to Learn More About Timing, Power, and IR Drop!

Location: Saint Tropez

**Embedded Tutorial 2B: Accelerated Safe and Secure Machine Learning**

Location: Monte Carlo

Session 2C: Architecting for Efficiency of Deep Learning

Location: Riveria

Special Session 2D: EDA for Cyber-Physical Systems

Location: Capri

4:00 - 4:30pm

Coffee Break

Location: Terrazza Foyer

4:15 - 5:45pm

Session 3A: Generate. Stimulate and Simulate!

Location: Saint Tropez

Session 3B: Sweet Memories of Deep Learning

Location: Monte Carlo

Session 3C: Adaptive Power and Precision Optimization Using Machine **Learning and Approximate Computing**

Location: Riveria

Special Session 3D: 2018 CAD Contest at ICCAD

Location: Capri

5:45 - 6:15pm

A New Era in Digital Routing

Location: Saint Tropez

Sponsored by: cadence

6:15 - 6:45pm

**Networking Reception**

Sponsored by: cadence

Location: Frescos Lounge

6:45 - 8:15pm

**ACM Student Research Competition Technical Presentations**

Location: Saint Tropez

## Opening Session and Awards

## Time: 8:30 - 10:00am | Location: Saint Tropez

Kick off the conference with opening remarks from the ICCAD Executive Committee members and hear the highlights of the conference. The IEEE/ACM William J. McCalla ICCAD Best Paper award will be announced along with other award presentations from IEEE and ACM.

### IEEE/ACM WILLIAM J. MCCALLA ICCAD BEST PAPER AWARD

This award is given in memory of William J. McCalla for his contributions to ICCAD and his CAD technical work throughout his career.

#### Front-End Award:

# 5C.1 DNNBuilder: An Automated Tool for Building High-Performance DNN Hardware Accelerators for FPGAs

Xiaofan Zhang - Univ. of Illinois at Urbana-Champaign

Junsong Wang - IBM Research - China Chao Zhu - IBM Research - China Yonghua Lin - IBM Research - China

JinJun Xiong - IBM T.J. Watson Research Center Wen-Mei Hwu - Univ. of Illinois at Urbana-Champaign Deming Chen - Univ. of Illinois at Urbana-Champaign

#### Back-End Award:

# 10B.1 PolyCleaner: Clean Your Polynomials Before Backward Rewriting to Verify Million-Gate Multipliers

Alireza Mahzoon - Universität Bremen Daniel Grosse - Universität Bremen / DFKI Rolf Drechsler - Universität Bremen / DFKI

## TEN YEAR RETROSPECTIVE MOST INFLUENTIAL PAPER AWARD

This award is being given to the paper judged to be the most influential on research and industrial practice in computer-aided design over the ten years since its original appearance at ICCAD.

### 2008 Paper Titled: A Low-Overhead Fault Tolerance Scheme for TSV-Based 3D Network on Chip Links

Igor Loi - University of Bologna

Subhasish Mitra - Thomas H. Lee, Stanford University

Shinobu Fujita - Toshiba

Luca Benini - *University of Bologna* ICCAD 2008, pp. 598 - 602

### 2018 ACM/SIGDA PIONEER AWARD

Alberto L. Sangiovanni-Vincentelli, Edgar L. and Harold H. Buttner Chair of Electrical Engineering and Computer Sciences at the University of California at Berkeley For pioneering and fundamental contributions to design automation research and industry in system-level design, embedded systems, logic synthesis, physical design and circuit simulation.

### IEEE CEDA OUTSTANDING SERVICE RECOGNITION

Sri Parameswaran - University of New South Wales

For outstanding service to the EDA community as ICCAD General Chair in 2017.

#### IEEE CEDA ERNEST S. KUH EARLY CAREER AWARD

Paul Bogdan - University of Southern California

For contributions to network-on-chip interconnects for multi-core cyber-physical systems.

# IEEE CAS TRANSACTIONS ON VERY LARGE SCALE INTEGRATION SYSTEMS PRIZE PAPER AWARD

# Paper entitled "Wireless NoC and Dynamic VFI Co-Design: Energy Efficiency without Performance Penalty"

Ryan Gary Kim, Wonje Choi, Zhuo Chen, Partha Pratim Pande, Diana Marculescu, and Radu Marculescu

## **ACM/SIGDA CADATHALON**

Introduction of the 2018 winners.

# KEYNOTE ADDRESS

Keynote: Adventures and Opportunities in Cyber-Physical Systems Research

Time: 9:00 - 10:00am | Location: Saint Tropez

Speaker: Chandra Krintz - Univ. of California, Santa Barbara

Through the convergence of recent advances in device and control systems, sensor networks, data analytics, and cloud computing, Cyber-physical systems (CPS) is on course to transform our society and disrupt the way humans engineer and interact with the world around them. CPS tightly integrates communications and computation into ordinary physical objects and amalgamates them as systems, enabling them to collect vast amounts of data about their environment, to extract inferences and predictions from the data, and to use this information to automate, enhance, actuate, control, and optimize operations and decision making at a variety of scales. In this talk, we discuss some of the key technological advances that are spurring CPS innovation, we detail our experiences employing CPS to optimize agricultural processes as part of the UCSB SmartFarm project, and we describe the opportunities and challenges that are emerging in CPS research.

**Biography:** Chandra Krintz is Professor of Computer Science at UC Santa Barbara and Chief Scientist and Co-founder of AppScale Systems Inc. Chandra holds M.S./Ph.D. degrees in CS from UC San Diego. Her research interests lie at the cross-section of cloud computing and programming systems and her contributions improve performance, reduce energy consumption, and simplify the use of heterogenous, distributed systems. Chandra has supervised and mentored over 60 students, published her work in a wide range of top venues, and participated in numerous outreach efforts to introduce computing to young people. Chandra's efforts have been recognized with a NSF CAREER award, the CRA-W Anita Borg Early Career Award, and the UCSB Academic Senate Distinguished Teaching Award. She was also named a Cloud Computing Pioneer by Information Week and a top M2M Woman by Connected World.

Coffee Break

Time: 10:00 - 10:30am | Room: Terrazza Foyer

# 1A - Analytical Techniques in Design Planning Time: 10:30am - 12:30pm | Room: Saint Tropez

#### Moderator:

Sabya Das - Synopsys, Inc.

The papers in this session propose techniques to address different challenges in the physical design flow. The first paper considers the thermal aspect of design during the floorplanning stage. The second paper proposes an analytical solution of Poisson's equation to solve global placement, and the third one suggests proximal group ADMM approach for foggy and proximity effects-aware placement. Finally, the fourth paper discusses efficient partitioning and grouping for Timing-driven Multiplexing in FPGA designs.

## 1A.1 A Fast Thermal-Aware Fixed-Outline Floorplanning Methodology Based on Analytical Models

Jai-Ming Lin, Tai-Ting Chen, Yen-Fu Chang, **Wei-Yi Chang** - National Cheng Kung Univ. Ya-Ting Shyu, Yeong-Jar Chang, Juin-Ming Lu - Industrial Technology Research Institute

# **1A.2\*** Analytical Solution of Poisson's Equation and Its Application to VLSI Global Placement Wenxing Zhu, **Zhipeng Huang**, Jianli Chen - Fuzhou Univ. Yao-Wen Chang - National Taiwan Univ.

1A.3 Novel Proximal Group ADMM for Placement Considering Fogging and Proximity Effects Jianli Chen, Li Yang, Zheng Peng, Wenxing Zhu - Fuzhou Univ. Yao-Wen Chang - National Taiwan Univ.

# 1A.4 Simultaneous Partitioning and Signal Grouping for Time-Division Multiplexing in 2.5D FPGA-Based Systems

$\textbf{Shih-Chun Chen} \cdot \textit{National Taiwan Univ}.$

Richard Sun - Synopsys, Inc.

Yao-Wen Chang - National Taiwan Univ.

# 1B - Ahoy! Anti-Piracy Techniques Time: 10:30am - 12:30pm | Room: Monte Carlo

#### Moderators:

Tauhidur Rahman - Univ. of Alabama Uiiwal Guin - Auburn Univ.

Piracy attacks have been threatening the IC industry. This session explores the new territories of trusted manufacturing in reversible computing, 3D ICs, analog mixed-signal, and timing countermeasures. The first paper explains how reversible circuits can be used to prevent piracy and reverse engineering. The second paper proposes an attack on timing locks. The third one extends the boundary of logic locking to analog and mixed-signal systems, and the last paper solves split manufacturing and camouflaging problems in 3D systems.

## 1B.1 IC/IP Piracy Assessment of Reversible Logic

Samah Saeed - City Univ. of New York Xiaotong Cui - Chongqing Univ. Alwin Zulehner, Robert Wille - Johannes Kepler Univ. Linz Rolf Drechsler - Universität Bremen Kaijie Wu, Ramesh Karri - New York Univ.

## 1B.2 TimingSAT: Timing Profile Embedded SAT Attack Abhishek Chakraborty, Yuntao Liu, Ankur Srivastava - Univ. of Maryland, College Park

1B.3 Towards Provably-Secure Analog and Mixed-Signal Locking Against Overproduction Nithyashankari Gummidipoondi Jayasankaran, Adriana Sanabria Borbon, Edgar Sanchez-Sinencio, Jiang Hu, Jeyavijayan Rajendran - Texas A&M Univ.

# 1B.4 Best of Both Worlds: Integration of Split Manufacturing and Camouflaging into a Security-Driven CAD Flow for 3D ICs

Satwik Patnaik - New York Univ.

Mohammed Ashraf, Ozgur Sinanoglu, Johann Knechtel - New York Univ., Abu Dhabi

All speakers are denoted in bold | \* denotes Best Paper Candidate

# 1C - Flexibility Makes Learning Better Time: 10:30am - 12:30pm | Room: Riveria

#### Moderator:

Deming Chen - Univ. of Illinois at Urbana-Champaign

Efficient training and deployment of neural networks are critical. The first paper in this session discusses a novel quantization scheme using powers-of-arbitrary-log-bases, and the second paper presents a processing in-DRAM framework for binary CNNs. The third paper proposes AXNet, a neural network based approximate computing allowing holistic end-to-end training. The last paper in this session proposes a scalable-effort CNN (ConvNet) that allows effort-accuracy scalability for classification of data at multi-level abstraction.

# 1C.1 Efficient Hardware Acceleration of CNNs Using Logarithmic Data Representation With Arbitrary Log-Base

Sebastian Vogel - Robert Bosch GmbH Mengyu Liang - Tech. Univ. of Munich Andre Guntoro - Robert Bosch GmbH Walter Stechele - Tech. Univ. of Munich Gerd Ascheid - RWTH Aachen Univ.

- 1C.2 NID: Processing Binary Convolutional Neural Network in Commodity DRAM Jaehyeong Sim, Hoseok Seol, Lee-Sup Kim - Korea Advanced Institute of Science and Technology

- **1C.3 AXNet: ApproXimate Computing Using an End-to-End Trainable Neural Network** Zhenghao Peng, **Li Jiang**, Xuyang Chen, Chengwen Xu, Naifeng Jing, Xiaoyao Liang, Cewu Lu *Shanghai Jiao Tong Univ.*

- 1C.4 Scalable-Effort ConvNets for Multilevel Classification

Valentino Peluso. Andrea Calimera Politecnico di Torino

# Special Session 1D - Emerging Reconfigurable Nanotechnologies: Can they Support Future Electronics?

Time: 10:30am - 12:30pm | Room: Capri

### Moderator:

Akash Kumar - Technische Univ. Dresden

Several emerging reconfigurable technologies have been explored in recent years offering device level runtime reconfigurability. These technologies offer the freedom to choose between p- and n-type functionality from a single transistor. In order to optimally utilize the feature-sets of these technologies, circuit designs and storage elements require novel design to complement the existing and future electronic requirements. An important aspect to sustain such endeavors is to supplement the existing design in, ow from the device level to the circuit level. This should be backed by a thorough evaluation so as to ascertain the feasibility of such explorations. Additionally, since these technologies offer runtime reconfigurability and often encapsulate more than one functions, hardware security features like camouflaging layouts and polymorphic logic gates come naturally cheap with circuits based on these reconfigurable technologies. This session presents innovative approaches to be devised for optimal circuit designs harnessing the reconfigurable features of these nanotechnologies. New circuit design paradigms based on these nano devices will be discussed to brainstorm on exciting avenues for novel computing elements.

## 1D.1 Introduction to Reconfigurable Nanotechnology

Patsy Cadareanu - Univ. of Utah

### 1D.2 EDA for reconfigurable Nanotechnology

Akash Kumar - Technische Univ. Dresden

## 1D.3 Blurring the Line Between Logic and Memory

Vijay Narayanan - Pennsylvania State Univ.

## 1D.4 Reconfigurable Emerging Nanotechnologies for Hardware Security

Xiaobo Sharon Hu - Univ. of Notre Dame

#### 1D.5 Paper Title Emerging Reconfigurable Nanotechnologies: Can They Support Future Electronics?

Shubham Rai - Technische Univ. Dresden

Srivatsa Rangachar - Pennsylvania State Univ.

Patricia Cadareanu - Univ. of Utah

Xunzhao Yin, Xiaobo Sharon Hu - Univ. of Notre Dame

Pierre-Emmanuel Gaillardon - Univ. of Utah

Vijay Narayanan - Pennsylvania State Univ.

Akash Kumar - Technische Univ. Dresden

# Additional Meeting - ACM Student Research Competition Poster Session

Time: 11:30am - 1:30pm | Room: Private Dining Room

Sponsored by Microsoft Research, the ACM Student Research Competition (SRC) is an internationally recognized venue enabling undergraduate and graduate students who are members of ACM and ACM SIGDA to:

- Experience the research world—for many undergraduates this is a first!

- Share research results and exchange ideas with other students, judges, and conference attendees.

- Rub shoulders with academic and industry luminaries.

- Understand the practical applications of their research.

- Perfect their communication skills. Receive prizes and gain recognition from ACM, and the greater computing community.

ACM SRC has three rounds:

- (1) abstract review

- (2) poster session (this session)

- (3) technical presentation

In the first round, 2-page research abstracts are evaluated by EDA experts from academia and industry to select participants for the second round (this session). For the ACM SRC at ICCAD 2018 competition, 20 participants were selected to present their research at ICCAD.

The posters are evaluated by EDA experts to select up to 5 participants in graduate and undergraduate categories to advance to the final round (technical presentation round). Students are expected to discuss their work with judges. Each judge will rate the student's visual presentation based on the criteria of uniqueness of the approach, the significance of the contribution, visual presentation, and quality of presentation.

More details can be found at: sigda.org/src

Sponsored by:

## Lunch

Time: 12:30 - 1:30pm | Room: Bayside Terrace

Join fellow attendees for lunch in Terrazza Ballroom.

# 2A - It's Time to Learn More About Timing, Power, and IR Drop!

Time: 1:45 - 3:45pm | Room: Saint Tropez

#### Moderator:

Chung-Kuan Cheng - Univ. of California, San Diego

This session covers the state of the art advances in timing, power, and IR drop analysis in both digital and analog design. Suitability in the end-to-end design methodology will be the feature focus, along with applications of machine learning to this challenging domain.

# 2A.1 Design and Algorithm for Clock Gating and Flip-Flop Co-Optimization Giyoung Yang, Taewhan Kim - Seoul National Univ.

# **2A.2** Macro-Aware Row-Style Power Delivery Network Design for Better Routability Jai-Ming Lin, Jhih-Sheng Syu, I-Ru Chen - National Cheng Kung Univ.

## 2A.3 Modeling and Optimization of Magnetic Core TSV-Inductor for On-Chip DC-DC Converter

Baixin Chen - Zhejiang Univ.

Umamaheswara Tida - Univ. of Notre Dame

**Cheng Zhuo** - Zhejiang Univ. Yiyu Shi - Univ. of Notre Dame

### 2A.4 Machine-Learning-Based Dynamic IR Drop Prediction for ECO

Yen-Chun Fang, Heng-Yi Lin, **Min-Yan Su**, Chien-Mo Li - *National Taiwan Univ.* Eric Jia-Wei Fang - *MediaTek, Inc.*

# Embedded Tutorial 2B - Accelerated Safe and Secure Machine Learning

Time: 1:45 - 3:45pm | Room: Monte Carlo

This tutorial brings the top experts from the industry and academia to cover several important topics in safe, and secure machine learning that enable automated synthesis of trustworthy machine learning for the state-of-the-art algorithms. The discussed topics include ML on private (encrypted) data, model assurance against the contemporary attacks including adversarial learning and transfer learning, IP protection for ML, as well as trusted execution of contemporary ML algorithms. Due to its prevalence and dominance in state-of-the-art applications, deep learning would be utilized as the proof-of-concept for the various discussed methodologies.

The tutorial provides a unique opportunity for the audience to gain a thorough understanding of deep learning models, the security, privacy and reliability issues of the existing methodologies, and potential solutions to address the standing issues in the context of (deep) learning models. Emphasis will be given to safe and secure automation and acceleration of the explained methodologies using hardware-software co-design techniques. Given the wide range of ML applications in various scientific fields and the increasing interest of academia and industry leaders in this emerging field, this tutorial prepares the audience to attain a competitive advantage by providing a holistic view of the existing security and privacy concerns in automated systems empowered by ML and the state-of-theart hardware-software co-design solutions to address those concerns.

## 2B.1 Deep Learning on Encrypted Data

Farinaz Koushanfar, M. Sadegh Riazi - Univ. of California, San Diego

### 2B.2 Machine Learning IP Protection

Rosario Cammarota - Qualcomm Technologies, Inc.

### 2B.3 Assured Deep Learning: Practical Defense Against Adversarial Attacks

**Bita Rouhani** - Microsoft Corporation

Mohammad Samragh, Mojan Javaheripi, Tara Javidi, Farinaz Koushanfar - Univ. of California, San Diego

### 2B.4 Trusted Execution for Machine Learning

Ahmad-Reza Sadeghi - Technische Univ. Darmstadt

# 2C - Architecting for Efficiency of Deep Learning Time: 1:45 - 3:45pm | Room: Riveria

#### Moderator:

Meng Li - Facebook AI Silicon Research

The papers of this session aim to improve the efficiency of deep learning systems via optimizing the architecture for hardware, algorithm, and design methodology. The first two papers propose new hardware architecture for deep neural network accelerators. The third paper designs a new neural network architecture for energy-constrained applications. The fourth paper presents neural network-based design methodology for timing error prediction.

## 2C.1 Tetris: Re-Architecting Convolutional Neural Network Computation for Machine Learning Accelerators

**Hang Lu**, Xin Wei, Ning Lin, Guihai Yan, Xiaowei Li - Chinese Academy of Sciences

## 2C.2 FCN-Engine: Accelerating Deconvolutional Layers in Classic CNN Processors

Dawen Xu, **Kaijie Tu** - Hefei Univ. of Technology Ying Wang - Chinese Academy of Sciences Heng Liu, Bingsheng He - National Univ. of Singapore Huawei Li - Chinese Academy of Sciences

# 2C.3 Designing Adaptive Neural Networks for Energy-Constrained Image Classification Dimitrios Stamoulis, Ting-Wu (Rudy) Chin, Anand Krishnan Prakash, Haocheng Fang, Sribhuvan Sajja, Mitchell Bognar, Diana Marculescu - Carnegie Mellon Univ.

# 2C.4 FATE: Fast and Accurate Timing Error Prediction Framework for Low Power DNN Accelerator Design

Jeff Zhang, Siddharth Garg - New York Univ.

# Special Session 2D - EDA for Cyber-Physical Systems Time: 1:45 - 3:45pm | Room: Capri

#### Moderators:

Samarjit Chakraborty - Technical Univ. of Munich Mohammad Al Faruque - Univ. of California, Irvine

From automating tasks in the domain of integrated circuits design, Electronic Design Automation (EDA) has been moving up the design abstraction ladder, now encompassing many system-level design tasks. The next challenge facing the EDA community is to develop methods and also tools for cyber-physical systems (CPS) design. However, currently available EDA tools and methods cannot handle these complex CPSs where the physical processes, the control algorithms and the computation and communication platforms are all modeled and designed in a tightly integrated fashion. There exists a gap between the communities dealing with different aspects of CPS design and the goal of this special session is to address these challenges in order to effectively design and validate large-scale CPSs. In particular, it will feature talks on four important CPS application areas and discuss the need for EDA methods and tools in these areas.

# 2D.1 Waterfall is Too Slow, Let's go Agile: Multi-Domain Coupling for Synthesizing Automotive Cyber-Physical Systems

Debayan Roy, Michael Balszun - Technical Univ. of Munich

**Thomas Heurung** - Siemens Industry Software GmbH, Germany

Samarjit Chakraborty - Technical Univ. of Munich

Amol Naik - Siemens Corp.

## 2D.2 Model-Based and Data-Driven Approaches for Building Automation and Control

Tianshu Wei - Univ. of California, Riverside

Xiaoming Chen - Chinese Academy of Sciences

Xin Li - Duke Univ.

Qi Zhu - Northwestern Univ.

### 2D.3 Future Automation Engineering Using Structural Graph Convolutional Neural Networks

Jiang Wan - Univ. of California, Irvine

Blake S. Pollard - Carnegie Mellon Univ.

Sujit Rokka Chhetri, Mohammad Abdullah Farugue - Univ. of California, Irvine

Arquimedes Canedo - Siemens Corp.

Palash Goyal - Univ. of Southern California

#### 2D.4 Design Automation for Battery Systems

Swaminathan Narayanaswamy, Sangyoung Park, Sebastian Steinhorst,

Samarjit Chakraborty - Technical Univ. of Munich

Coffee Break

Time: 3:45pm - 4:15pm | Room: Terrazza Foyer

## 3A - Generate, Stimulate and Simulate!

Time: 4:15 - 5:45pm | Room: Saint Tropez

#### Moderator:

Nagaraj Kelageri - Qualcomm Technologies, Inc.

Effective generation of stimuli is a critical step in the verification flow. The three papers in this session present advances in this field. The first paper is focused on coverage-directed testing in FPGA environments using the insights developed in software verification. The second paper speeds the generation of directed tests for shared-memory multi-processor verification. The third paper presents a method that facilitates rapid generation of multiple and diverse stimuli from complex constraints.

## 3A.1 RFUZZ: Coverage-Directed Fuzz Testing of RTL on FPGAs

**Kevin Laeufer**, Jack Koenig, Donggyu Kim, Jonathan Bachrach, Koushik Sen - *Univ. of California*, *Berkeley*

# 3A.2 Steep Coverage-Ascent Directed Test Generation for Shared-Memory Verification of Multicore Chips

**Gabriel Andrade**, Marleson Graf, Nícolas Pfeifer, Luiz Dos Santos - *Federal Univ. of Santa Catarina*

# 3A.3 SMTSampler: Efficient Stimulus Generation from Complex SMT Constraints Rafael Dutra, Jonathan Bachrach, Koushik Sen - Univ. of California, Berkeley

3B - Sweet Memories of Deep Learning

# Time: 4:15 - 5:45pm | Room: Monte Carlo

#### Moderator:

Yanzhi Wang - Northeastern Univ.

Who doesn't remember the basics of deep learning! But can you design systems for in-memory computing using FeFETs that reduce power consumption and ReRAM that moderates data migration? The first paper in this session investigates reliable ReRAM-based deep learning with single-bit cells. The second paper introduces a power-efficient FeFET-based in-memory computing architecture, whereas the third paper designs and implements a system for multitask (transfer) learning using GPUs and ReRAM. Even as you learn new things, important information should stay in your memory!

## 3B.1 DL-RSIM: A Simulation Framework to Enable Reliable ReRAM-Based Accelerators for Deep Learning

Meng-Yao Lin - National Taiwan Univ.

Hsiang-Yun Cheng - Academia Sinica

Wei-Ting Lin, Tzu-Hsien Yang, I-Ching Tseng, Chia-Lin Yang - *National Taiwan Univ.* Han-Wen Hu, Hung-Shen Chang, Hsiang-Pang Li - *Macronix International Co., Ltd.* Meng-Fan Chang - *National Tsing Hua Univ.*

# **3B.2** A Ferroelectric FET Based Power-Efficient Architecture for Data-Intensive Computing Yun Long, Taesik Na, Prakshi Rastogi, Karthik Rao, Asif Islam Khan, Sudhakar Yalamanchili, Saibal Mukhopadhyay - *Georgia Institute of Technology*

# 3B.3 EMAT: An Efficient Multi-Task Architecture for Transfer Learning Using ReRAM Fan Chen Hai Li - Duke Univ

# 3C - Adaptive Power and Precision Optimization Using Machine Learning and Approximate Computing

Time: 4:15 - 5:45pm | Room: Riveria

#### Moderator:

Elaheh Bozorgzadeh - Univ. of California, Irvine

This session includes three papers which propose adaptive algorithms to optimize the energy efficiency and fixed-point precision. The first paper presents a novel reinforcement learning approach to co-optimize the power delivery and consumption of multicore systems. The second paper considered power-hungry augmented reality applications on mobile devices and presents an automated technique to minimize energy consumption without degrading the quality. Finally, the last paper employs a Q-Learning algorithm to adaptively optimize the precision of stochastic gradient descent in deep neural network (DNN) training.

# 3C.1 Co-Manage Power Delivery and Consumption for Manycore Systems Using Reinforcement Learning

**Haoran Li**, Zhongyuan Tian, Rafael Kioji Vivas Maeda, Xuanqi Chen, Jun Feng, Jiang Xu Rafael Kioji Vivas Maeda, Xuanqi Chen, Jun Feng, Jiang Xu - *The Hong Kong University of Science and Technology*

# 3C.2 Adaptive-Precision Framework for SGD Using Deep Q-Learning Wentai Zhang, Hanxian Huang, Jiaxi Zhang, Ming Jiang, Guojie Luo - Peking Univ.

## 3C.3 Differentiated Handling of Physical Scenes and Virtual Objects for Mobile Augmented Reality

**Chih-Hsuan Yen**, Wei-Ming Chen - National Taiwan Univ. Pi-Cheng Hsiu - Academia Sinica Tei-Wei Kuo - National Taiwan Univ.

# Special Session 3D - 2018 CAD Contest at ICCAD Time: 4:15 - 5:45pm | Room: Capri

The CAD Contest at ICCAD (https://iccad-contest.org/) is a challenging, multi-month, research and development competition, focusing on advanced, real-world problems in the field of Electronic Design Automation (EDA). Contestants can participate in one or more problems provided by EDA/ IC industry. The prizes will be awarded at an ICCAD special session dedicated to this contest. Since 2012, the CAD Contest at ICCAD has been attracting more than a hundred teams per year (112 teams from 12 regions in 2015, 135 teams from 11 regions in 2016, and 123 teams from 10 regions in 2017), fostering productive industry-academia collaborations, and leading to hundreds of publications in top-tier conferences and journals. The contest keeps enhancing its impact and boosts EDA research.

- 3D.1 Overview of 2018 CAD Contest at ICCAD

- Mark Po-Hung Lin National Chung Cheng Univ.

- 3D.2 A: Smart EC: Program-Building for Name Mapping Chi-An (Rocky) Wu Cadence Design Systems, Inc.

- 3D.3 Problem B: Obstacle-Aware On-Track Bus Routing About Liao Synopsys, Inc.

- 3D.4 Problem C: Timing-Aware Fill Insertion Bo Yang Synopsys, Inc.

- **3D.5** Paper Title: DATC RDF: An Academic Flow From Logic Synthesis to Detailed Routing Jinwook Jung Korea Advanced Institute of Science and Technology

Iris Hui-Ru Jiang - National Taiwan Univ.

Jianli Chen - Fuzhou Univ.

Shih-Ting Lin, Yih-Lang Li - National Chiao Tung Univ.

Victor Kravets, Gi-Joon Nam - IBM Research

# Additional Meeting - A New Era in Digital Routing Time: 5:45 - 6:15pm | Room: Saint Tropez

**Speaker: Wen-Hao Liu** - Cadence Design Systems, Inc.

Routing problem becomes more and more complicated for the advanced technology nodes. If the design flow is not fully aware of routability, the design most likely cannot be fabricated at the end of the flow due to routability issues. This talk will introduce the modern routing challenges faced by digital design practitioners in the industry, and the speaker will share his experience about how to improve routability awareness for digital design tools from logical syntheses to detailed routing.

**Biography:** Wen-Hao Liu, received his Ph.D. degree in Computer Science from National Chiao Tung University, Taiwan in 2013. His research interests include routing, placement, and clock synthesis. Wen-Hao has published more than 30 papers and 5 patents in these fields, and he has served on the technical program committee of DAC, ICCAD, ISPD, and ASPDAC. Currently, Wen-Hao works at Cadence as a software architect. He is the main developer of the next-generation routing engines used in multiple Cadence's tools, and he has involved in the technology node enablement for 16nm, 10nm, 7nm, 5nm, and 3nm.

Sponsored by: Cadence

# **Networking Reception**

Time: 6:15 - 6:45pm | Room: Frescos Lounge

Whatever your goal, networking receptions are the perfect venue for you to expand your network and keep you connected! Join us today to catch up with your colleagues and discuss the day's presentations with the conference presenters. All attendees are invited.

Sponsored by:

# <u>cādence</u>

ACADEMIC NETWORK

# Additional Meeting - ACM Student Research Competition Technical Presentations

Time: 6:45 - 8:15pm | Room: Saint Tropez

The ACM Student Research Competition allows both graduate and undergraduate students to discuss their research with student peers, as well as academic and industry researchers, in an informal setting, while enabling them to attend ICCAD.

This session is the final round of ACM SRC at ICCAD 2018. Each student will present for 10 minutes, followed by a 2-minute question and answer period. This session will be attended by the evaluators and any interested conference attendees. The top three winners in each category will be chosen based on these presentations. The undergraduate and graduate finalists will be eligible to compete in the ACM SRC Grand Finals to be held in June 2019.

More details can be found at: sigda.org/src

# TUESDAY SCHEDULE

8:30 - 10:00am

Session 4A: Device Optimization for Reliability and Performance

Enhancement

Location: Saint Tropez

Session 4B: Clean Up Your Data

Location: Monte Carlo

**Special Session 4C: Security of Emerging Architectures**

Location: Riveria

Special Session 4D: Machine Learning for Electronic Design Automation:

Modeling, Optimization, and Resilience

Location: Capri

10:00 - 10:30am

**Coffee Break**

**Location: Capri** Spon.

Sponsored by: HUAWEI

10:30am - 12:00pm

Session 5A: The Non-Unified Theory of Approximate Computing

Location: Saint Tropez

Session 5B: Resistance is Not Futile (for RAM)

Location: Monte Carlo

Session 5C: High-Performance Deep Learning Accelerators on FPGAs

Location: Riveria

Special Session 5D: Hardware Intellectual Property (IP) Protection

Techniques: What, When, and How to Use?

Location: Capri

Special Session 5E: Managing Heterogeneous Many-Cores for High-

Performance and Energy-Efficiency

Location: Private Dining Room

12:00 - 12:30pm

Lunch

Location: Terrazza Ballroom

12:30 - 1:30pm

CEDA Invited Keynote: Analyzing the Disruptive Impact of a Silicon Compiler

**Andreas Olofsson** - Defense Advanced Research Projects Agency

Location: Terrazza Ballroom

# TUESDAY SCHEDULE

1:45 - 3:45pm

Session 6A: Deep Dive into Mixed Size Cell Placement

Location: Saint Tropez

Session 6B: Post-CMOS Technologies and Emerging Applications

Location: Monte Carlo

Session 6C: Biochips, Blockchain, and Learning in CPS

Location: Riveria

Special Session 6D: Is Adversarial Learning a Threat for Machine Learning? Defense Strategies and Design of Better Machine Learners!

Location: Capri

**Embedded Tutorial 6E: Majority Logic Synthesis**

Location: Private Dining Room

3:45 - 4:15pm

Coffee Break

4:15 - 6:15pm

Session 7A: Routing: The Devil is in the Details

Location: Saint Tropez

Session 7B: Synthesizing Neural, Parallel, and Approximate Logic

Location: Monte Carlo

Session 7C: Build a Fort: Designing and Assessing Secure Architectures

Location: Riveria

Special Session 7D: Security for Next-Generation Connected and **Autonomous Vehicles**

Location: Capri

Embedded Tutorial 7E: The Need and Opportunities of Electromigration-Aware Integrated Circuit Design

Location: Private Dining Room

6:15 - 6:45pm

**Networking Reception**

Location: Frescos Lounge

Sponsored by:

6:45 - 8:30pm

**ACM/SIGDA Member Meeting**

Location: Terrazza Ballroom

# 4A - Device Optimization for Reliability and Performance Enhancement

Time: 8:30 - 10:00am | Room: Saint Tropez

#### Moderator:

Takashi Sato - Kyoto Univ.

This session presents enhanced modeling and analysis to improve performance in a variety of devices while accounting for the effects of noise and aging induced delay increases. The first paper presents a novel analytical model of static noise margin in SRAM cells. The second paper enhances the reliability of circuits by handling transistor aging through adaptive voltage guardbanding with online monitoring. The last paper presents models for analyzing the variation of transistor characteristics in flexible electronics, and proposes practical methods for its compensation.

# 4A.1 Physical Modeling of Bitcell Stability in Subthreshold SRAMs for Leakage-Area Optimization Under PVT Variations

Xin Fan - RWTH Aachen Univ.

Rui Wang - Intrinsic ID

Tobias Gemmeke - RWTH Aachen Univ.

# 4A.2 Comparing Voltage Adaptation Performance Between Replica and In-Situ Timing Monitors

Yutaka Masuda - Osaka Univ.

Jun Nagayama, Hirotaka Takeno, Yoshimasa Ogawa, Yoichi Momiyama - *Socionext, Inc.* Masanori Hashimoto - *Osaka Univ.*

# 4A.3 Strain-Aware Performance Evaluation and Correction for OTFT-Based Flexible Displays Tengtao Li, Sachin S. Sapatnekar - Univ. of Minnesota

## 4B - Clean Up Your Data

## Time: 8:30 - 10:00am | Room: Monte Carlo

#### Moderator:

Tulika Mitra - National Univ. of Singapore

This session focuses on managing data in a secure and energy-efficient manner for SSD storage and bus-based communication architectures. The papers in this session propose novel strategies for fast sanitization of data in MLC Flash memory, secure data placement in SSDs, and energy-efficient approximations when sending data over on-chip buses.

### 4B.1 Achieving Fast Sanitization with Zero Live Data Copy for MLC Flash Memory

**Ping-Hsien Lin** - Macronix International Co., Ltd.

Yu-Ming Chang - National Taiwan Univ.

Yung-Chun Li, Wei-Chen Wang - Macronix International Co., Ltd.

Chien-Chung Ho - National Chung Cheng Univ.

Yuan-Hao Chang - Academia Sinica

### 4B.2 Architecting Data Placement in SSDs for Efficient Secure Deletion Implementation

Hoda Aghaei Khouzani - Univ. of Delaware

Chen Liu - Intel Corp.

Chengmo Yang - Univ. of Delaware

#### 4B.3 AxBA: An Approximate Bus Architecture Framework

Jacob R. Stevens. Ashish Ranian. Anand Raghunathan - Purdue Univ.

# Special Session 4C - Security of Emerging Architectures Time: 8:30 - 10:00am | Room: Riveria

#### Moderator:

Farinaz Koushanfar - Univ. of California, San Diego

Computing of tomorrow will critically rely on radically new architectural paradigms, driven by a new set of applications, including deep learning, real-time classification of massive arrays of sensor data, comprehension and pattern recognition in big-data sets. Emerging architectures offer tremendous advantages with respect to various design objectives, but one important target has been neglected so far: security. Adversarial attacks can target a system's communication links, the software running on it, and the humans using it. However, the system's hardware is increasingly considered its Achille's heel, as more and more at-tacks targeting the physical implementation of security-relevant functions. Recent purely hardware-oriented attacks called Meltdown and Spectre compromised millions of installed systems. The proposed session will consider the intricate relationship between emerging architectures and security from two sides. The first two talks will focus on security implications of novel architectural concepts: approximate computing and neuromorphic multi-processor SoCs. These paradigms are currently discussed without considering security, although systems designed according to these principles are well-suitable for security-critical tasks, like area surveillance or intrusion detection. The third talk will take a different approach: How should highly complex heterogeneous systems be designed when security is taken into account from the beginning? Security solutions discussed in the session will have to be addressed by holistic strategies where CAD tools will play a main role

## 4C.1 Security: The Dark Side of Approximate Computing?

**Francesco Regazzoni**, Cesare Alippi - *Univ. of Lugano* Ilia Polian - *Univ. of Stuttgart*

#### 4C.2 Security Aspects of Neuromorphic MPSoCs

**Johanna Sepulveda** - Technical Univ. of Munich Cezar Reinbrecht - Delft Univ. of Technology Jean-Philippe Diguet - Centre National de la Recherche Scientifique

### 4C.3 Vulnerability-Tolerant Secure Architectures

**Todd Austin**, Valeria Bertacco, Baris Kasikci - *Univ. of Michigan* Sharad Malik - *Princeton Univ.* Mohit Tiwari - *Univ. of Texas at Austin*

# Special Session 4D - Machine Learning for Electronic Design Automation: Modeling, Optimization, and Resilience

Time: 8:30 - 10:00am | Room: Capri

#### Moderator:

Pande Partha - Washington State University

The rate of growth of Big Data, slowing down of Moore's law, and the rise of emerging applications pose significant challenges in the design of large-scale computing systems with high-performance, energy-efficiency, and reliability. This special session will consider solutions based on machine learning and data analytics to address the following challenges: (1) How can we model the performance and power consumption of heterogeneous systems and interconnects using machine learning techniques? (2) How to use machine learning and statistical modeling for effective design space exploration of computing systems to optimize for power, performance, and thermal metrics? (3) How to use machine learning techniques to efficiently manage resources of computing systems (e.g., power, memory, interconnects) to improve performance and energy-efficiency? (4) How can data analytics facilitate fault diagnosis, detect anomalies, and increase robustness in the network backbone of emerging large-scale networking systems? To address these outstanding challenges, out-of-the-box approaches need to be explored. By integrating machine learning algorithms, data analytics, statistical modeling, and design of advanced computing systems, this session will engage a broad section of ICCAD conference attendees. This special session is targeted towards university researchers/professors, students, industry professionals, and computing system designers. This session will attract newcomers who want to learn how to apply machine learning and data analytics to solve problems in computing systems, as well as experienced researchers looking for exciting new directions in computing systems design, EDA methodologies, and multi-scale computing. This special session covers design, optimization and resilience: three main pillars of designing computing systems. It also highlights how machine learning and EDA researchers can join hands to design energy-efficient and reliable chips and systems.

- **4D.1** Machine Learning for Performance and Power Modeling of Heterogeneous Systems Joseph Greathouse, Gabriel Loh Advanced Micro Devices, Inc.

- 4D.2 Machine Learning for Design Space Exploration and Optimization of Manycore Systems Ryan Gary Kim - Colorado State Univ.

Janardhan Rao Doppa, Partha Pratim Pande - Washington State Univ.

- 4D.3 Failure Prediction Based on Anomaly Detection for Complex Core Routers

Shi Jin - Duke Univ. Zhaobo Zhang - Huawei Technologies Co., Ltd. **Krishnendu Chakrabarty** - Duke Univ. Xinli Gu - Huawei Technologies Co., Ltd.

Coffee Break

Time: 10:00am - 10:30am | Room: Terrazza Foyer

# 5A - The Non-Unified Theory of Approximate Computing Time: 10:30am - 12:00pm | Room: Saint Tropez

#### Moderator:

Nektarios Tsoutsos - Univ. of Delaware.

This session deals with trading off computational accuracy and energy efficiency. The first paper explores a novel classifier-approximator architecture for approximate computing on a low-power accelerator. The second paper advocates a new approach based on stochastic computing to trade off accuracy and circuit level efficiency. The final paper advocates a theoretically-robust methodology for optimizing multi-output approximate logic.

# 5A.1 Invocation-Driven Neural Approximate Computing with aMulticlass-Classifier and Multiple Approximators

Haiyue Song, Li Jiang, Chengwen Xu, Zhuoran Song, Naifeng Jing,

Xiaoyao Liang - Shanghai Jiao Tong Univ.

Qiang Xu - The Chinese University of Hong Kong

## 5A.2 Deterministic Methods for Stochastic Computing Using Low-Discrepancy Sequences M. Hassan Najafi, David Lilja, Marc Riedel - Univ. of Minnesota

# 5A.3 Design Space Exploration of Multi-Output Logic Function Approximations Jorge Echavarria, Stefan Wildermann.

Jürgen Teich - Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU)

# 5B - Resistance is Not Futile (for RAM) Time: 10:30am - 12:00pm | Room: Monte Carlo

#### Moderator:

Chengmo Yang - Univ. of Delaware

Resistive RAM (ReRAM) is an emerging non-volatile storage and near-memory computing solution that promises to disrupt traditional computing as we know it. The papers in this session propose a robust hybrid ReRAM fabric, explore the use of energy-efficient and fast logic implementations in ReRAM fabrics, and the use of ReRAM in executing emerging deep learning workloads.

## 5B.1 3DICT: A Reliable and QoS Capable Mobile Process-In-Memory Architecture for Lookup-Based CNNs in 3D XPoint ReRAMs

Qian Lou - Indiana University Bloomington Wujie Wen - Florida International Univ.

**Lei Jiang** - Indiana University Bloomington

#### 5B.2 Aliens: A Novel Hybrid Architecture for Resistive Random-Access Memory

**Bing Wu**, Dan Feng, Wei Tong, Jingning Liu, Shuai Li, Mingshun Yang, Chengning Wang, Yang Zhang - *HuaZhong University of science and technology*

#### 5B.3 FELIX: Fast and Energy-Efficient Logic in Memory

**Saransh Gupta** - Univ. of California, San Diego Mohsen Imani - University of California San Diego Tajana Rosing - Univ. of California, San Diego

# 5C - High-Performance Deep Learning Accelerators on FPGAs

Time: 10:30am - 12:00pm | Room: Riveria

#### Moderator:

Yingyan Lin - Rice Univ.

For both edge-devices and cloud servers, FPGA accelerators for deep neural networks have delivered favorable reconfigurability and performance. However, long hardware design time, prior homogeneous designs, and irregularities in deep learning algorithms have limited the achievable throughput and latency. To address these, the papers in this session present automated RTL generation with fine-grained pipelining, hardware-optimized algorithm adaptation, and integration of heterogeneous accelerators.

# 5C.1\* DNNBuilder: An Automated Tool for Building High-Performance DNN Hardware Accelerators for FPGAs

**Xiaofan Zhang** - Univ. of Illinois at Urbana-Champaign Junsong Wang, Chao Zhu, Yonghua Lin - IBM Research - China Jinjun Xiong - IBM T.J. Watson Research Center Wen-Mei Hwu, Deming Chen - Univ. of Illinois at Urbana-Champaign

# 5C.2 Algorithm-Hardware Co-Design of Single Shot Detector for Fast Object Detection on FPGAs

**Yufei Ma** - Arizona State Univ. Tu Zheng - Fuzhou Univ. Yu Cao, Sarma Vrudhula, Jae-Sun Seo - Arizona State Univ.

### 5C.3 TGPA: Tile-Grained Pipeline Architecture for Low Latency CNN Inference

**Xuechao Wei**, Yun (Eric) Liang - Peking Univ. Xiuhong Li - Peking University, Beijing Cody Hao Yu - Univ. of California, Los Angeles Peng Zhang - Falcon Computing Solutions, Inc. Jason Cong - Univ. of California, Los Angeles

# Special Session 5D - Hardware Intellectual Property (IP) Protection Techniques: What, When, and How to Use?

Time: 10:30am - 12:00pm | Room: Capri

#### Moderator:

Ozgur Sinanoglu - New York Univ., Abu Dhabi

Globalization of Integrated Circuit (IC) design is forcing the IC/IP designers and users re-assess their trust in hardware. As the IC design flow spans the globe, driven by cost-conscious consumer electronics, hardware is increasingly prone to new kinds of attacks such as counterfeiting, hardware Trojans, side channel analysis, reverse engineering and IP piracy. An attacker, anywhere within this design flow, can reverse engineer the functionality of an IC/IP, steal and claim ownership of the IP, inject malicious circuitry (i.e., hardware Trojans) into the IC, or introduce counterfeits into the supply chain. Moreover, an untrusted IC fab may overbuild ICs and sell them illegally. The semiconductor industry is estimated to lose \$4 billion annually due to these attacks.

Many of these attacks hinge on the fact the attacker can obtain full control over the design. To thwart such adversaries, researchers have developed several techniques, namely IP metering, logic locking/encryption, camouflaging, and split manufacturing. These techniques are currently being used and/or considered for usage by companies. These techniques greatly differ in their threat models and security properties. Together, they address a wide spectrum of attackers—untrusted designer, untrusted foundry, untrusted testing facility, untrusted user, and a combination thereof.

This tutorial brings in three experts on these topics to explain these techniques in a collective and cohesive way. The tutorial will explain what techniques to use against attackers, when to use them in the supply-chain, and how to use them in a provably-secure way. Techniques will be explained using concepts from IC design and test, graph theory, and cryptography. The presenters collectively have more than two decades of research experience in these topics, providing a wide coverage from theory to practice.

## 5D.1 IP Protection in Untrusted Supply Chain

Farinaz Koushanfar - Univ. of California, San Diego

### 5D.2 Customized Locking of IP Blocks on a Multi-Million-Gate SoC

**Ozgur Sinanoglu** - New York Univ., Abu Dhabi Abhrajit Sengupta - New York Univ.

Mohammed Nabeel, Mohammed Ashraf - New York Univ., Abu Dhabi

#### 5D.3 Split Manufacturing

Jeyavijayan Rajendran - Texas A&M Univ.

# Special Session 5E - Managing Heterogeneous Many-Cores for High-Performance and Energy-Efficiency

Time: 10:30am - 12:00pm | Room: Private Dining Room

### Moderator:

Siddharth Garg - New York Univ.

Heterogeneity has become the Swiss army knife for designing energy-efficient and thermally safe systems ranging from simple edge devices to high-performance multi-core processing platforms. Integration of application-specific heterogeneous accelerators and general-purpose cores deliver programmable systems-on-chip (SoCs) with superior performance and significantly lower power footprint compared to homogenous architectures. This special session presents the state-of-theart in form of three talks covering Resource Managment, Online learning and Communication Architectures for heterogeneous Many-Cores.

## 5E.1 Dynamic Resource Management for Heterogeneous Many-Cores

**Jörg Henkel** - Karlsruhe Institute of Technology **Jürgen Teich**, Stefan Wildermann - Friedrich-Alexander-Univ. Erlangen-Nürnberg Hussam Amrouch - Karlsruhe Institute of Technology

# **5E.2** Online Learning for Adaptive Optimization of Heterogeneous SoCs Ganapati Bhat, Sumit Mandal, Umit Ogras - Arizona State Univ.

Ujjwal Gupta - Intel Corp.

# **5E.3** Hybrid On-Chip Communication Architectures for Heterogeneous Manycore Systems Biresh Kumar Joardar, Janardhan Rao Doppa, Partha Pratim Pande - Washington State Univ. Diana Marculescu, Radu Marculescu - Carnegie Mellon Univ.

## Lunch

Time: 12:00 - 1:30pm | Room: Terrazza Ballroom

Join fellow attendees for lunch in Terrazza Ballroom.

# CEDA Invited Luncheon Talk - Analyzing the Disruptive Impact of a Silicon Compiler

Time: 12:30 - 1:30pm | Room: Terrazza Ballroom

Speaker: **Andreas Olofsson** - Defense Advanced Research Projects Agency

Recent years have seen an explosion in the cost and time required to design advanced System-on-Chips (SoCs), systems-in-packages (SiPs), and PCBs. As part of the \$1.5B Electronics Resurgence Initiative (ERI), DARPA is building the world's first general purpose silicon compilers. The effort involves two distinct research programs, the Intelligent Design of Electronic Assets (IDEA) program aiming to create a no-human-in-the-loop layout generator for digital and analog circuits, and the Posh Open Source Hardware (POSH) program aiming to create a high quality trustable open source ecosystem. Together the efforts will create a universal hardware compiler capable of automatically generating production ready GDSII drawings directly from rich catalog of trustable source code and schematics for digital as well as analog circuits. Achieving this ambitious goal will require advancing the state of the art in machine learning, optimization algorithms, expert systems, and verification technology. This talk will discuss technical challenges associated with building a universal hardware compiler and provide analysis of potential economic and societal impacts.

Biography: Mr. Andreas Olofsson joined DARPA as a program manager in the Microsystems Technology Office in January 2017. His interests include intelligent design automation, system optimization, and open hardware. Prior to his arrival at DARPA, Mr. Olofsson devoted 20 years to designing and testing low-power processors and mixed-signal circuits at Texas Instruments, Analog Devices, and Adapteva. Chip products designed by Mr. Olofsson include low-power digital signal processors (DSPs), charge-coupled device (CCD) readout circuits, and massively parallel reduced instruction set computing (RISC) processors. From 2008 to 2016, Mr. Olofsson served as the CEO of Adapteva, where he developed the Epiphany architecture and Parallella open source computer. The Parallella democratized access to parallel computing and catalyzed the growth of a community of 10,000 developers and 200 universities across the globe. Mr. Olofsson received his Bachelor of Science in Physics and Electrical Engineering and Master of Science in Electrical Engineering from the University of Pennsylvania. Mr. Olofsson is a member of IEEE and holds nine U.S. patents.

## 6A - Deep Dive into Mixed Size Cell Placement

Time: 1:45 - 3:45pm | Room: Saint Tropez

#### Moderator:

Ismail Bustany - Xilinx Inc.

In the physical design placement implementation flow, mixed-height cells introduce additional challenges, such as Poly-alignment, fence regions, multi-cell spacing, and technology constraints. In this session, the first paper addresses the challenges involving the multi-cell spacing constraint. The remaining three papers address the problems related to technology and fence region constraints.

- **6A.1** A Practical Detailed Placement Algorithm under Multi-Cell Spacing Constraints

Yu-Hsiang Cheng, Ding-Wei Huang, Wai-Kei Mak, Ting-Chi Wang National Tsing Hua Univ.

- **6A.2** Mixed-Cell-Height Placement Considering Drain-to-Drain Abutment Yu-Wei Tseng, Yao-Wen Chang National Taiwan Univ.

- **6A.3** Mixed-Cell-Height Legalization Considering Technology and Region Constraints Ziran Zhu, Xingquan Li, Yuhang Chen, Jianli Chen, Wenxing Zhu Fuzhou Univ. Yao-Wen Chang National Taiwan Univ.

- **6A.4** Mixed-Cell-Height Placement with Complex Minimum-Implant-Area Constraints Jianli Chen, Peng Yang, Xingquan Li, Wenxing Zhu Fuzhou Univ. Yao-Wen Chang National Taiwan Univ.

### 6B - Post-CMOS Technologies and Emerging Applications Time: 1:45pm - 3:45pm | Room: Monte Carlo

#### Moderator:

Deliang Fan - Univ. of Central Florida

This session covers the post-CMOS technologies and the related emerging applications. The resistive memory (memristor) device is proposed as the enabling technology for main memory, routing switch in FPGA, and synaptic weight in neural network accelerators. An Ising processor with approximated parallel tempering is proposed to improve the quality of optimization solutions.

- **6B.1** RAPID: Read Acceleration for Improved Performance and Endurance in MLC/TLC NVMs Poovaiah Manavattira Palangappa, Kartik Mohanram Univ. of Pittsburgh

- 6B.2 Sneak Path Free Reconfiguration of Via-Switch Crossbars Based FPGA Ryutaro Doi, Jaehoon Yu, Masanori Hashimoto Osaka Univ.

- 6B.3 Mixed Size Crossbar based RRAM CNN Accelerator with Overlapped Mapping Method Zhenhua Zhu, Jilan Lin Tsinghua Univ.

Ming Cheng - EE departement of tsinghua university

Lixue Xia, Hanbo Sun - Tsinghua Univ.

Xiaoming Chen - Chinese Academy of Sciences

Yu Wang, Huazhong Yang - Tsinghua Univ.

**6B.4** Enhancing the Solution Quality of Hardware Ising-Model Solver via Parallel Tempering Hidenori Gyoten, Masayuki Hiromoto, Takashi Sato - Kyoto Univ.

## 6C - Biochips, Blockchain, and Learning in CPS Time: 1:45 - 3:45pm | Room: Riveria

#### Moderators:

Umit Ogras - Arizona State Univ.

Mohammad Al Faruque - Univ. of California, Irvine

Cyber-Physical Systems serve as the fabric of modern and future intelligent world. The first two papers of the session covers Artificial Neural Networks as enabler for CPS, one on the hardening of deep neural networks against adversarial attacks, and the other on reinforcement learning for wearable devices. The third and fourth papers are on two emerging applications of CPS, biochips and blockchain.

#### 6C.1\* Defensive Dropout for Hardening Deep Neural Networks Under Adversarial Attacks

Siyue Wang - Northeastern Univ.

Xiao Wang - Boston Univ. Pu Zhao - Northeastern Univ.

Wujie Wen - Florida International Univ.

David Kaeli - Northeastern Univ.

Peter Chin - Boston Univ.

Xue Lin - Northeastern Univ.

#### 6C.2 Online Human Activity Recognition Using Low-Power Wearable Devices

Ganapati Bhat, Ranadeep Deb, Vatika Vardhan Chaurasia - Arizona State Univ.

Holly Shill - Barrow Neurological Institute

Umit Y. Ogras - Arizona State Univ.

#### 6C.3 Shadow Attacks on MEDA Biochips

Mohammed Shayan - New York Univ.

Sukanta Bhattacharjee - New York Univ., Abu Dhabi

Tung-Che Liang - Duke Univ.

Jack Tang - New York Univ.

Krishnendu Chakrabarty - Duke Univ.

Ramesh Karri - NYU

#### 6C.4 LeapChain: Efficient Blockchain Verification for Embedded IoT

Emanuel Regnath - Tech. Univ. of Munich

Sebastian Steinhorst - Technical Univ. of Munich, Nanyang Technological Univ.

# Special Session 6D - Is Adversarial Learning a Threat for Machine Learning? Defense Strategies and Design of Better Machine Learners!

Time: 1:45 - 3:45pm | Room: Capri

#### Moderators:

Houman Homayoun - George Mason Univ. Sam Gu - FutureWei Technologies, Inc.

In the recent years, Machine Learning (ML) especially mammalian brain inspired neural networks (including deep neural networks (DNNs)) have demonstrated an impressive performance and robustness to noise in different domains ranging from medical imaging, autonomous driving to defense applications. Despite DNNs being robust to noise and perturbations, recent research works have exploited the vulnerabilities and showed that the DNNs can be fooled by adding specially crafted perturbations to the input. In this session, first talk will introduce the challenges of ML in adversarial settings. This will be followed by two talks on making the ML inference robust to adversarial attacks in robotics and security domains. The last talk will provide an analysis of different adversarial attacks and solution to improve the efficiency of existing defense techniques.

## 6D.1 Robust Object Estimation using Generative-Discriminative Inference for Secure Robotics Applications

Zhefan Ye, Odest Chadwicke Jenkins, Shiyang Lu, Zhiqiang Sui - *Univ. of Michigan* **R. Iris Bahar**, Alessandro Costantini, Yanqi Liu - *Brown Univ.*

#### 6D.2 Adversarial Evasion Resilient Hardware Malware Detectors

Dmitry Ponomarev - Binghamton Univ. Khaled Khasawneh - Univ. of California, Riverside Lei Yu - Binghamton Univ.

Nael Abu-Ghazaleh - Univ. of California, Riverside

## 6D.3 Efficient Utilization of Adversarial Training towards Robust Machine Learners and its Analysis

Sai Manoj, Sairaj Amberkar, Setareh Rafatirad, Houman Homayoun - George Mason Univ.

## Embedded Tutorial 6E - Majority Logic Synthesis Time: 1:45 - 3:45pm | Room: Private Dining Room

#### Moderator:

Mathias Soeken - École Polytechnique cole Polytechnique Fédérale de Lausanne

The majority function evaluates to true, if at least two of its Boolean inputs evaluate to true. The majority function has frequently been studied as a central primitive in logic synthesis applications for many decades. Knuth refers to the majority function in the last volume of his seminal The Art of Computer Programming as "probably the most important ternary operation in the entire universe." Majority logic sythesis has recently regained signficant interest in the design automation community due to nanoemerging technologies which operate based on the majority function. In addition, majority logic synthesis has successfully been employed in CMOS-based applications such as standard cell or FPGA mapping. The tutorial gives a broad introduction ito the field of majority logic synthesis. It will review fundamental results and describe recent contributions from theory, practice, and applications.

#### **6E.1** Practical Majority Logic Synthesis

**Luca Amarù** - Synopsys, Inc.

#### **6E.2** Decomposing n-ary Majority Functions

Eleonora Testa, Mathias Soeken,

Winston Haaswijk - École Polytechniquecole Polytechnique Fédérale de Lausanne

Luca Amarù - Synopsys, Inc.

Giovanni De Micheli - École Polytechnique Fédérale de Lausanne

#### **6E.3** Efficient Normal Form Systems for Representing Boolean Functions

Miguel Couceiro - Univ. of Lorranie

Erkko Lehtonen - Technische Univ. Dresden

Pierre Mercuriali, - Univ. of Lorranie

Abdallah Saffidine - Australian National University

## 6E.4 Overview of Emerging Non-Charge-Based Majority Logic Technologies

Odysseas Zografos - IMEC

#### **6E.5** Majority Logic Synthesis

Luca Amarù - Synopsys. Inc.

Eleonora Testa - École Polytechnique cole Polytechnique Fédérale de Lausanne

Miguel Couceiro - Univ. of Lorranie

Odysseas Zografos - IMEC

Giovanni De Micheli - École Polytechniquecole Polytechnique Fédérale de Lausanne

Mathias Soeken - École Polytechnique Fédérale de Lausanne

Coffee Break

Time: 3:45 - 4:15pm | Room: Terrazza Foyer

## 7A - Routing: The Devil is in the Details Time: 4:15 - 6:15pm | Room: Saint Tropez

#### Moderator:

Gracieli Posser - Cadence Design Systems, Inc.

Continuous technology node shrinking and the increased complicated design rules have made detailed routing one of the most contentious parts of the physical design. In this session, the first paper discusses machine learning based routing congestion and violation prediction methods. This is followed by two papers on initial detailed routing. The session concludes with a paper on an open net locator for ECO routing.

## 7A.1 RouteNet: Routability Prediction for Mixed-Size Designs Using Convolutional Neural Network

Zhiyao Xie - Duke Univ.

Yu-Hung Huang, Guan-Qi Fang - National Taiwan Univ. of Science and Technology

Haoxing Ren - NVIDIA Corp.

Shao-Yun Fang - National Taiwan Univ. of Science and Technology

Yiran Chen - Duke Univ. Jiang Hu - Texas A&M Univ.

## **7A.2** [Anonymous]: An Initial Detailed Router for Advanced VLSI Technologies Andrew Kahng, Lutong Wang, Bangqi Xu - Univ. of California, San Diego

#### 7A.3 A Multithreded Initial Detailed Routing Algorithm Considering Global Routing Guides Fan-Keng Sun, Hao Chen, Chen-Hao Hsu, Ching-Yu Chen,

Yao-Wen Chang - National Taiwan Univ.

## 7A.4 Extending ML-OARSMT to Net Open Locator with Efficient and Effective Boolean Operations

Bing-Hui Jiang, **Hung-Ming Chen** - National Chiao Tung Univ.

## 7B - Synthesizing Neural, Parallel, and Approximate Logic Time: 4:15 - 6:15pm | Room: Monte Carlo

#### Moderator:

Paras Gupta - Qualcomm Technologies, Inc.