FROM CHIPS TO SYSTEMS - LEARN TODAY, CREATE TOMORROW

# CONFERENCE PROGRAM & EXHIBITS GUIDE

Sponsored by:

# GETTE DACAPPI

# **DOWNLOAD FOR FREE!**

GET THE LATEST INFORMATION RIGHT WHEN YOU NEED IT.

DAC.COM

- Search the Technical Program

- Find Exhibitors

- Create Your

Personalized Schedule

Thank you to our DAC Mobile App Sponsor:

Ingenuity for life

Visit DAC.com for more details and to download the FREE app!

# GENERAL CHAIR'S WELCOME -

Dear Colleagues,

Viva Las Vegas! Welcome to the 56th Design Automation Conference, back in town for the first time since 2001. Las Vegas bills itself as the entertainment capital of the world, and this week the city is also the design automation capital of the world!

DAC is a unique event that brings together the entire design and design automation ecosystem, from academic and industrial researchers, to designers, developers, vendors and educators. You're a part of that, so what should you do this week? Take advantage of DAC's unique character.

The DAC executive committee, along with the hundreds of volunteers who put the conference together, have once again brought you an excellent program with top quality research papers, great keynotes and invited talks, exciting panels, and valuable insights from design practitioners.

Beyond that, though, you should take advantage of all that DAC offers. Attend a presentation on a topic you don't know. DAC covers everything from emerging devices to cloud computing, so there's bound to be something. Find a new product or service. Ask questions. Attend our many social functions and meet up with old friends or make some new ones. And don't forget to take advantage of our location – there's always something going on in Las Vegas, and this week one of the highlights is DAC!

Enjoy the #56DAC!

Rob Aitken

#### **ACM/SIGDA**

#### **IEEE/COUNCIL ON ELECTRONIC DESIGN AUTOMATION**

# TABLE OF CONTENTS •

| General Chair's Welcome1                   | Tuesday SKY Talk38                            |

|--------------------------------------------|-----------------------------------------------|

| Conference Sponsors1                       | Tuesday Designer/IP Track Poster Session 49   |

| Conference Information 3                   | Tuesday Work-in-Progess Poster Session 51     |

| Networking Receptions4                     | Wednesday Keynote54                           |

| Keynotes5                                  | Wednesday Sessions 55                         |

| Visionary & SKY Talks7                     | Wednesday Designer/ IP Track 58               |

| In Memory9                                 | Wednesday SKY Talk 60                         |

| 2019 Awards10                              | Wednesday Designer/IP Track Poster Session 71 |

| DAC Pavilion – Booth 87111                 | Wednesday Work-in-Progess Poster Session72    |

| Sunday Workshops & Additional Meetings 13  | Late Breaking Results74                       |

| Monday Opening Session 18                  | Thursday Awards Ceremony75                    |

| Monday Visionary Talk18                    | Thursday Keynote75                            |

| Monday Keynote18                           | Thursday Sessions                             |

| Monday Designer/ IP Track19                | Thursday is Training Day 86                   |

| Monday SKY Talk20                          | Colocated Conferences 88                      |

| Monday Designer/IP Track Poster Session 25 | Additional Meetings89                         |

| Monday Tutorials27                         | Platinum, Gold & Silver Sponsors 97           |

| Tuesday Opening Session30                  | Exclusive Sponsorships                        |

| Tuesday Keynote30                          | Exhibitor List                                |

| Tuesday Sessions31                         | Design Infrastructure Alley – Booth 1137 100  |

| Tuesday Designer/ IP Trac35                |                                               |

# CONTERENCE INFORMATION •

#### **EXHIBIT HOURS**

#### **LOCATION: EXHIBIT HALLS N3 & N4**

Monday, June 3 10:00am - 6:00pm Tuesday, June 4 10:00am - 6:00pm Wednesday, June 5 10:00am - 6:00pm

#### **REGISTRATION HOURS**

### LOCATION: LAS VEGAS CONVENTION CENTER LEVEL 2

Friday, May 31 - Saturday June 1 8:00am - 6:00pm Sunday, June 2 - Wednesday June 5 7:00am - 7:00pm Thursday, June 6 7:00am - 5:00pm

Thank you to our Co-Sponsors:

#### **ONLINE PROCEEDINGS**

DAC Proceedings and tutorials will be delivered electronically online via a username and password.

To access: http://proceedings.dac.com

Username = Email address

Password = Registration ID (on your badge)

Please refer to your registration receipt to be reminded of what package and associated files you are eligible to view.

#### **STAY CONNECTED**

#### **WIRELESS INTERNET**

Connect to the complimentary wireless network at "DAC-Free-WiFi-by-Siemens"

Thank you to our Sponsor:

#### "BIRDS-OF-A-FEATHER" MEETINGS

DAC will provide conference rooms for informal groups to discuss items of common technical interest. These very informal, non-commercial meetings, held after hours, are referred to as "Birds-of-a-Feather" (BOF).

All BOF meetings are held at the Las Vegas Convention Center Tuesday, June 4 from 7:00 - 8:30pm.

To arrange a BOF Meeting, please email Sophia Sun at sophia@dac.com

#### **FIRST AID ROOM**

First Aid and Security are located in the lobby area outside the DAC Exhibit Floor and have roving personnel around the entire perimeter of the facility. In case of emergencies dial from your phone 702-892-7400 which will connect you to the command center.

First Aid Room Hours:

Monday, June 3: 9:00am - 7:00pm Tuesday, June 4: 9:00am - 7:00pm Wednesday, June 5: 9:00am - 6:00pm

#### **DAC MOBLE APP**

Download the DAC App!

Review the conference program, find exhibitors, and create a personalized schedule all from your phone or mobile device.

The DAC App is **FREE** for registered attendees! Check your email for your personalized invite or visit DAC.com for more information

Thank you to our DAC Mobile App Sponsor:

SIEMENS

Ingenuity for life

# DACNETWORKING OPPORTUNITIES

#### WELCOME RECEPTION

**Sunday, June 2 6:00 - 7:30pm | Westgate Hotel - Ballroom A**Join fellow attendees for the first event to network and kick-off DAC 2019

#### **NETWORKING RECEPTION**

**Monday, June 3 6:00 - 7:00pm | Exhibit Floor**Join us on the Exhibit Floor and enjoy snacks and beverages.

Thank you to our Reception Sponsor:

#### **DESIGN INFRASTRUCTURE ALLEY RECEPTION**

Monday, June 4

5:00 - 6:00pm | Design-on-Cloud Pavilion

Join us on the Exhibit Floor and enjoy snacks and beverages.

### NETWORKING RECEPTION AND WORK-IN-PROGRESS POSTER SESSION

**Tuesday, June 4 6:00 - 7:00pm | Exhibit Floor**Join us on the Exhibit Floor to see Work-in-Progress posters and enjoy light snacks and beverages.

Thank you to our Reception Sponsor:

### NETWORKING RECEPTION AND WORK-IN-PROGRESS POSTER SESSION

Wednesday, June 5 6:00 - 7:00pm | Level 2 Pre-Function Area

Join us in the Level 2 Lobby to see Work-in-Progress posters and enjoy light snacks and beverages.

Thank you to our Reception Sponsor:

Music courtesy of:

# KEYNOTE PRESENTATIONS -

# **KEYNOTE:** SECURING THE BILLIONS OF DEVICES AROUND US

**GALEN C. HUNT** – Distinguished Engineer and Managing Director - Microsoft Corporation, Redmond, WA

Monday, June 3 || Time: 9:20 - 10:00am || Keynote Booth 1145

The next decade promises the democratization of connectivity to every device. Significant drops in the cost of connectivity mean that every form of electrical device—every child's toy, every household's appliances, and every DoD

sensor—will become connected to the Internet. Tens of billions of these devices are controlled by microcontrollers, a class of device particularly ill-prepared for the security challenges of internet connectivity. What is required to secure these billions of devices? And, how can it be done economically enough to apply to every device? See page 18 for more details.

### **KEYNOTE: HORS D'OEUVRES FROM CHAOS**

**THOMAS DOLBY** – Musician, Producer & Innovator - Johns Hopkins Univ., Baltimore, MD

Tuesday, June 4 | | 9:20 - 10:00am | | Keynote Booth 1145

As a boy, what Thomas Dolby loved most about synthesizers was that (quote) "they did things I didn't expect." Just from fooling around with synths and samplers, never reading the owner's manual (there was none!), he learned all that he knows about 'real' music and musical instruments. But his frustration today is that electronic music has not embraced the advances in Al and deep learning that are now become infused in filmmaking, videogames and virtual reality. Loops

and samples, he says, are like "dumb Lego blocks that have no knowledge of each other"; yet schools of fish, murmurations of sparrows, and even world-class orchestral players watch and listen intently and make microsecond-grain, synaptic decisions, enabling them to think like a collective hive mind. Why then do synthesizers still have to behave like typewriters?

See page 30 for more details.

# **KEYNOTE:** PRIORITIZING PLAY IN AN AUTOMATED AGE

**JOHN COHN** – Massachusetts Institute of Technology & IBM Watson Al Lab, Cambridge, MA

Wednesday, June 5 | | 8:45 - 9:15am | | Keynote Booth 1145

John Cohn is an IBM Fellow in the MIT-IBM Watson Al Research Group based in Cambridge, MA. John earned a BSEE MIT, and a Ph.D in Computer Engineering from Carnegie Mellon University He has authored more than 30 technical

papers, contributed to four books and has more than 100 worldwide patents. In 2005 John was elected a Fellow of the IEEE.

John is active in education issues at a local, state and national level. He is so passionate about promoting STEM careers that he spent 59 days living and inventing in an abandoned steel mill as part of Discovery Channel's technical survival show "The Colony". John lives with his family in a restored 19th century schoolhouse in Jonesville Vermont and is eager to share his love of science and technology with anyone who will listen.

See page 54 for more details.

# KEYNOTE PRESENTATIONS

# KEYNOTE: FROM STUDENT PROJECT TO TACKLING THE MAJOR CHALLENGES IN REALIZING SAFE & SUSTAINABLE ELECTRIC VEHICLES

BAS VERKAIK – Founder, SPIKE, Eindhoven, The Netherlands Wednesday, June 5 11 9:20 – 10:00am 11 Keynote Booth 1145

In 2014, a group of students from the Eindhoven University of Technology set a clear goal to ride around the world in 80 days on an electric motorcycle to show the world what electric vehicles were capable of. Since a suitable motorcycle to undertake such a tour didn't exist yet, the Dutch students decided to entirely develop it by themselves. A revolutionary vehicle was the result: 400 km range from a self-developed swappable and modular battery pack. After completing the 80-day world tour late 2016, the unique knowledge and experience gained in this project was made commercial by founding the spinoff SPIKE Technologies. SPIKE aims to accelerate the transition towards safe & clean mobility by designing & developing high quality powertrain components for electric vehicles. Among these components are SPIKE's battery solutions, that distinguish themselves due to their safety, performance and lifetime, while they can be produced very cost-efficiently due to their unique design. Until now, SPIKE has supported in the development of a wide variety of electric vehicles and recently established its own battery production facility in the Netherlands.

In his talk, Bas Verkaik will explain the complex design decisions that had to be made in developing the electric motorcycle and they now have to make every day to cope with the rapidly changing developments in the electric vehicle market.

See page 54 for more details.

# **KEYNOTE:** REVERSE ENGINEERING VISUAL INTELLIGENCE

JAMES DICARLO, MD, PHD – Massachusetts Institute of Technology, Cambridge, MA

Thursday, June 6 || 9:20 - 10:00am || Room: N250

The brain and cognitive sciences are hard at work on a great scientific quest — to reverse engineer the human mind and its intelligent behavior. These field are still in their infancy. Not surprisingly, forward engineering approaches that aim to emulate human intelligence (HI) in artificial systems (AI) are also still in their infancy. Yet the intelligence and cognitive flexibility apparent in human behavior are an existence proof that machines can be constructed to emulate and work alongside the human mind. And history suggests that these challenges of reverse engineering human intelligence will be solved by tightly combining the efforts of brain and cognitive scientists (hypothesis generation and data acquisition), and forward engineering aiming to emulate intelligent behavior (hypothesis instantiation and data prediction). As this approach discovers the correct neural network models, those models will not only encapsulate our understanding of complex brain systems, they will be the basis of next-generation computing and novel brain interfaces for therapeutic and augmentation goals (e.g., brain disorders).

In this session, I will focus on one aspect of human intelligence — visual object categorization and detection — and I will tell the story of how work in brain science, cognitive science and computer science converged to create deep neural networks that can support such tasks. These networks not only reach human performance for many images, but their internal workings are modeled after— and largely explain and predict — the internal workings of the primate visual system. Yet, the primate visual system (HI) still outperforms current generation artificial deep neural networks (AI), and I will show recent new clues that the brain and cognitive sciences can offer. More broadly, our species is at the beginning of its most important science and engineering quest — the quest to understand and emulate human intelligence — and I hope to motivate others to engage that frontier alongside us.

See page 75 for more details.

# VISTONARY & SKY TALKS

### VISIONARY TALK: GAME CHANGERS: HOW AUTOMATION HAS CHANGED THE GAMING INDUSTRY

**Mark Yoseloff, Ph.D.** – Executive Director, UNLV Center for Gaming Innovation Univ. of Nevada, Las Vegas, NV

Monday, June 3 | | 9:00 - 9:20am | | Keynote Booth 1145

**Biography:** Mark Yoseloff, Ph.D. is the Executive Director of the UNLV Center for Gaming Innovation. The Center is dedicated to teaching and mentoring the next generation of innovators in the gaming

industry. Dr. Yoseloff is the retired chairman of the board and CEO of Shuffle Master, Inc., a NASDAQ Global Markets Company. He is currently the CEO of High Roller Productions, LLC, the Managing Member of Well

Suited, LLC, a product creation company, and a Managing Member of Big Bet Gaming, LLC, a product distribution company

Dr. Yoseloff holds BA and MA degrees from the University of Pennsylvania and a doctorate in mathematics from Princeton University. He is the coauthor of a college text entitled "Finite Mathematics" and holds well over 200 issued or pending patents throughout the world related to the gaming industry. See page 18 for more details.

### SKY TALK: WHAT CAN EDA DO FOR QUANTUM COMPUTING AND WHAT CAN QC DO FOR EDA?

**Leon Stok** — Vice President of IBM's Electronic Design Automation Group, Poughkeepsie, NY

Monday, June 3 | 1:00 - 1:45pm | DAC Pavilion - Booth 871

**Biography:** Leon Stok is Vice President of IBM's Electronic Design Automation group. His team delivers world-class design

and verification flows and tools being used to design the world's largest supercomputers, IBM systemZ and Power systems. Prior to this he held positions as director of EDA and executive assistant to IBM's Senior Vice President of Technology and Intellectual Property and executive assistant to IBM's Senior Vice President of the Technology group. Leon Stok studied electrical engineering at Eindhoven University of Technology, the Netherlands, from which he graduated with honors in 1986. He obtained a Ph.D. degree from Eindhoven University in 1991. At IBM's Thomas J. Watson Research Center, Leon Stok pioneered logic synthesis, as part of the team that developed BooleDozer. Subsequently, he managed IBM's synthesis group and drove the first commercial application of physical synthesis by developing IBM's Placement Driven Synthesis tool. From

1999-2004 he led all of IBM's design automation research as the Senior Manager Design Automation at IBM Research. He drove key innovations in DFM using RRR (Radically Restrictive Rules) in static timing analysis using statistical timing and in large block physical synthesis. Dr. Stok has presented over sixty keynotes, invited talks and tutorials at major IEEE and ACM conferences worldwide and at many leading universities. Dr. Stok has published over sixty papers on many aspects of high level, architectural and logic synthesis, low power design, placement driven synthesis and on the automatic placement and routing for schematic diagrams. He holds 13 patents in EDA. He was elected an IEEE fellow for the development and application of high-level and logic synthesis algorithms. See page 20 for more details.

# VISHONARY & SKY TALKS

### SKY TALK: MARCH OF THE MACHINES - BUILDING ETHICAL AI

Carolyn Herzog – Arm, Ltd., San Jose, CA

Tuesday, June 4 | | 1:00 - 1:45pm | | DAC Pavilion - Booth 871

**Biography:** Carolyn Herzog has over 20 years of global business and legal experience. She has extensive expertise in cybersecurity and privacy, ethics and compliance, corporate governance, regulatory compliance, crisis management, stakeholder engagement, and strategic

planning.

Carolyn is the Executive Vice President, General Counsel, Corporate Secretary and Chief Compliance Officer at Arm, the world's leading semiconductor IP company. At Arm, Carolyn leads a team of legal and public affairs professionals, and is responsible for all legal matters in the company. Prior to joining Arm, Carolyn was the VP, Chief Compliance Officer and Deputy General Counsel at Symantec Corporation, the global leader in cybersecurity, based in the company's headquarters in Mountain View, California. She held various roles at Symantec, leading the company through significant transformation in 3 major offices. Carolyn was instrumental in leading numerous acquisition integrations for Symantec and, notably, the company's sale of Veritas in 2016, creating a separate,

privately held company. As Head of Legal for the Europe, Middle East and Africa region, Carolyn was based in Symantec's European headquarters in the U.K. She joined Symantec through the AXENT Technologies acquisition in December 2000, where she successfully led the public company acquisition of AXENT by Symantec, as General Counsel. Carolyn had been based in the Washington DC area prior to moving to the UK, having worked in the international development arena, both in the non-profit sector and with The World Bank.

Carolyn has served on the European Board of the Association of Corporate Counsel, the Board for the National Cyber Security Alliance, and is an Advisory Board member to IPWatch System Corporation. She has been recognized as a Distinguished General Counsel by the Director's Roundtable, and an Attorneys Who Matter by Ethisphere Magazine.

Carolyn graduated from the University of Wisconsin, Madison with a JD and received her B.A. from Washington University in St. Louis. See page 38 for more details.

#### **SKY TALK: THE MEMORY FUTURES**

Gurtej S. Sandhu — Micron Technology, Inc., Boise, ID

Wednesday, June 5 | 1:00 - 1:45pm | DAC Pavilion - Booth 871

Biography: Gurtej Sandhu is Senior Fellow and Vice President at Micron Technology. In his current role, he is responsible for Micron's end-to-end R&D technology roadmaps and to drive cross-functional alignment across various departments and business units to proactively identify

technology gaps and managing the engineering organization to resource and execute on developing innovative technology solutions for future memory scaling. Dr. Sandhu's responsibilities include leading several internal project teams worldwide and managing interactions with research consortia around the world. He has held several engineering and management roles and is actively involved with a broad range of process technologies for IC processing and has pioneered several process

technologies currently employed in mainstream semiconductor chip manufacturing.

Dr. Sandhu received a degree in electrical engineering at the Indian Institute of Technology, New Delhi, and a Ph.D. in physics at the University of North Carolina, Chapel Hill, in 1990. He holds over 1,300 U.S. patents and is recognized as one of the top inventors in the world. A Fellow of IEEE, he received the prestigious IEEE Andrew S. Grove Award in 2018 for outstanding contributions to solid-state devices and materials technology, as well as for leadership, originality, breadth, among other achievements. This competitive award is presented annually by the IEEE Board of Directors to an individual with pioneering achievements to the semiconductor technology. See page 60 for more details.

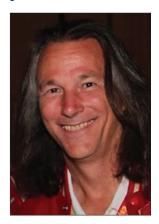

# Joe Daniels | 1959 - 2018

The EDA industry suffered a tremendous loss with the sudden passing of Joe Daniels in November, 2018. Many of us crossed paths with him in some way or another during the nearly 40 years he spent as a consultant, technical writer and editor in the industry. Most of his contributions were in project development, coordination, and software and hardware technical writing and editing. He consulted with many companies and organizations in the industry over the years, and had long-standing relationships with the IEEE-Standards Association and Accellera Systems Initiative. He touched many of the standards in use today, as well as many currently in development, with his admirable editing skills for technical content, consistency, style, and formatting. Joe was involved in editing and documenting more than 20 standards including ALF, DPCS, IP-XACT, SystemC-AMS, SystemVerilog, UVM, Verilog, PSS, SCE-MI, SystemC CCI, just to name a few. We are fortunate to have known Joe and to be the beneficiaries of his many contributions to the EDA community.

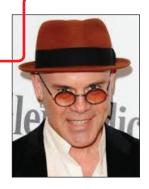

# Chuck Grindstaff, Siemens | 1957 - 2018

Former Siemens' PLM chief, Chuck Grindstaff passed away suddenly on Tuesday, October 23, 2018, at the age of 61. He won an Oscar award in 2004 for contributions to the evolution of digital audio editing technology. He presented a keynote at the 54th DAC in 2017. Chuck is a highly skilled PLM expert and left a permanent footprint in our industry. His humility, and his ability to listen and produce concise analyses serve as exemplary characteristics for all of us.

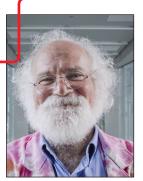

# Stuart Sutherland | 1953 - 2018

Stuart Sutherland passed away the summer of 2018, shortly after DAC. Stu was known as the wizard and consultant in SystemVerilog and UVM Training. He was the president of Sutherland HDL, Inc., with over 25 years of experience as a world expert and educator in hardware design language. In addition to being a key technical contributor to the IEEE 1364 and IEEE 1800 standards, he was a technical editor in merging 1364 and SystemVerilog 3.0 from Accellera into IEEE 1800. The word "Herculean" might come close to describing his work. His efforts continued as editor through the most recent release of IEEE 1800. Stu was one of the premier independent Verilog educators in our industry as well as a prolific author of books and technical papers. He is the author of numerous papers and books which have left a marked technical legacy in his field. Stuart is survived by his wife of 37 years and their five children as well as ten grandchildren. He will be greatly missed but never forgotten.

# 2019 AWARDS

The 56th DAC will recognize success and excellence for the following individuals in the field of design automation of electronic systems.

### 2018 PHIL KAUFMAN AWARD FOR DISTINGUISHED CONTRIBUTIONS TO ELECTRONIC SYSTEMS DESIGN

Thomas W. Williams, Consultant, Synopsys (retired), Synopsys Fellow

For Overall Impact on Electronics Industry through Contributions to Scan Design for Testability, Related Test Automation

### ACM IEEE A. RICHARD NEWTON TECHNICAL IMPACT AWARD IN ELECTRONIC DESIGN AUTOMATION

Edward B. Eichelberger, IBM (retired) IBM Fellow, IEEE Fellow Thomas W. Williams, Consultant, Synopsys (retired), Synopsys Fellow

For the paper "A Logic Design Structure for LSI Testability," In Proc. of the 14th Design Automation Conference, 1977

### 2019 MARIE R. PISTILLI WOMEN IN ENGINEERING ACHIEVEMENT AWARD

Iris Bahar - Professor of Engineering and Computer Science, Brown Univ.

#### P.O. PISTILLI UNDERGRADUATE SCHOLARSHIP FOR ADVANCEMENT IN COMPUTER SCIENCE AND ELECTRICAL ENGINEERING

**Gia Douglass**

#### **DAC UNDER-40 INNOVATORS AWARD**

The Under-40 Innovators Award is sponsored by Association for Computing Machinery (ACM), and the Institute of Electrical and Electronics Engineers (IEEE). The award will recognize the top five young innovators (nominees should be 40 years or younger in age as of June 1, 2019) who are movers and shakers in the field of design and automation of electronics.

#### **SYSTEM DESIGN CONTEST WINNERS**

#### **HACK@DAC WINNERS**

# CEDA HONORS LAURENCE NAGEL FOR THE DONALD O. PEDERSON SOLID-STATE CIRCUITS AWARD AS KEY CONTRIBUTOR TO THE SPICE SIMULATOR CREATION

Laurence W. Nagel, President, Omega Enterprises Consulting

### IEEE CEDA OUTSTANDING SERVICE AWARD

X. Sharon Hu, University of Notre Dame

For outstanding service to the EDA community as DAC General Chair in 2018.

#### **IEEE FELLOW**

**Deming Chen, University of Illinois at Urbana- Champaign** For contributions to FPGA high-level synthesis

#### **IEEE FELLOW**

Hai (Helen) Li, Duke University

For contributions to neuromorphic computing system

#### **IEEE FELLOW**

Farinaz Koushanfar, University of California, San Diego

For contributions to hardware and embedded systems security, and to privacy-preserving computing

#### IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS DONALD O. PEDERSON BEST PAPER AWARD

To Be Announced

#### **2019 ACM TODAES BEST PAPER AWARD**

Philipp Mundhenk, Andrew Paverd, Artur Mrowca, Sebastian Steinhorst, Martin Lukasiewycz, Suhaib A. Fahmy, and Samarjit Chakraborty,

"Security in Automotive Networks: Lightweight Authentication and Authorization," ACM Trans. Des. Autom. Electron. Syst. 22, 2, Article 25 (March 2017), 27 pages. DOI: https://doi.org/10.1145/2960407

#### **ACM SIGDA DISTINGUISHED SERVICE AWARD**

To Be Announced

### ACM SIGDA OUTSTANDING NEW FACULTY AWARD Jeyavijayan (JV) Rajendran, Texas A&M University

### ACM SIGDA OUTSTANDING PH.D. DISSERTATION AWARD

"Distributed Timing Analysis"

By Tsung-Wei Huang, Advisor: Martin D. F. Wong, University of Illinois at Urbana-Champaign

#### **BEST RESEARCH PAPER NOMINEES**

#### 11.1 - Accuracy vs. Efficiency: Achieving Both through FPGA-Implementation Aware Neural Architecture Search

Weiwen Jiang, Xinyi Zhang, Edwin Sha, Lei Yang, Qingfeng Zhuge, Yiyu Shi, Jingtong Hu (see page 32)

### 31.1 - BRIC: Locality-based Encoding for Energy-Efficient Brain-Inspired Hyperdimensional Computing

Mohsen Imani, Justin L. Morris, John Messerly, Helen Shu, Yaobang Deng, Tajana Rosing (see page 44)

### 40.1 - A 1.17 TOPS/W, 150fps Accelerator for Multi-face Detection and Alignment

Huiyu Mo, Leibo Liu, Wenping Zhu, Qiang Li, Hong Liu, Wenjing Hu, Yao Wang, Shaojun Wei (see page 55)

#### 51.2 - LithoGAN: End-to-end Lithography Modeling with Generative Adversarial Networks

Stephan Wei Ye, Mohamed Baker Alawieh, Yibo Lin, David Z. Pan (see page 61)

### 54.1 - DREAMPlace: Deep Learning Toolkit-enabled GPU Acceleration for Modern VLSI Placement

Yibo Lin, Shounak Dhar, Wuxi Li, Haoxing Ren, Brucek Khailany, David Z. Pan (see page 63)

# DACRALLON - BOOTH 871

Thank you to our DAC Pavilion Sponsor:

cādence

Monday, June 3

#### **FUNDAMENTAL SHIFTS IN THE ELECTRONICS ECOSYSTEM**

Date: Monday, June 3 | Time: 10:30 - 11:15am | DAC Pavilion - Booth 871

**SPEAKER:**

Wally Rhines - Mentor, A Siemens Business, Wilsonville, OR

### STRAIGHT TALK WITH TONY HEMMELGARN, SIEMENS DIGITAL INDUSTRIES SOFTWARE CEO

Date: Monday, June 3 | Time: 11:30am - 12:00pm | DAC Pavilion - Booth 871

**MODERATOR:**

Ed Sperling - Semiconductor Engineering, San Jose, CA

# HEY ALEXA, WHO SHOULD I TALK TO ABOUT IMPLEMENTING LOW-POWER, ALWAYS-ON WAKE-UP APPLICATIONS?

Date: Monday, June 3 | | Time: 2:00 - 2:45pm | | DAC Pavilion - Booth 871 Event Type: DAC Pavilion | | Keywords: IoT, Low Power, Emerging Technologies

Topic Area: Design, Embedded Systems & Software (ESS)

**MODERATOR:**

Brian Fuller - Arm, Ltd., San Jose, CA

ORGANIZER:

Jan Willis - Calibra Consulting, Menlo Park, CA

#### YOUNG UNDER 40 INNOVATORS AWARD PANEL

Date: Monday, June 3 | Time: 3:00 - 3:45pm | DAC Pavilion - Booth 871

MODERATOR:

Junko Yoshida - EE Times, Manhasset, NY

**ORGANIZER:**

Michelle Clancy - Cayenne Communication, Sunnyvale, CA

Topic of Discussion: Quantum Computing, Al and IOT: what do they have in common?

Please join EE Times editor Junko Yoshida for a lively discussion with the recipients of the 2019 Young Under 40 Innovator Award. Panelist will discuss the commonality between quantum computing, Al and IoT. The winners of the Young under 40 Innovators Award will be announced on Monday, June 3 during the opening session in the Keynote ballroom on the exhibition floor.

#### **DAC BINGO**

Date: Monday, June 3 | Time: 4:30 - 5:00pm | DAC Pavilion - Booth 871

**Tuesday, June 4**

#### THE STATE OF EDA: A VIEW FROM WALL STREET

Date: Tuesday, June 4 | | Time: 10:30 - 11:15am | | DAC Pavilion - Booth 871

SPEAKER:

Jay Vleeschhouwer - Griffin Securities, Inc., New York, NY

| Keynotes  | SKY Talks                | Research Sessions | Designer/IP<br>Track Sessions | Panels     | DAC Pavilion     | Monday Tutorials |

|-----------|--------------------------|-------------------|-------------------------------|------------|------------------|------------------|

| Workshops | Thursday is Training Day | Poster Sessions   | Additional Meetings           | Networking | Special Sessions | Design-on-Cloud  |

Thank you to our DAC Pavilion Sponsor: Cadence

# MYTH VS. REALITY: WHAT 5G IS SUPPOSED TO BE, AND WHAT IT WILL TAKE TO GET THERE

Date: Tuesday, June 4 | Time: 11:30am - 12:00pm | DAC Pavilion - Booth 871

**MODERATOR:**

Ed Sperling - Semiconductor Engineering, San Jose, CA

#### **INCORPORATION OF SECURITY INTO CHIP DESIGN (DARPA)**

Date: Tuesday, June 4 | | Time: 2:00 - 2:45pm | | DAC Pavilion - Booth 871

**Keywords: Security & Privacy**

SPEAKER: Serge Leef - Defense Advanced Research Projects Agency, Wilsonville, OR

#### ML/DL/AI FOR EDA: A MYTH OR A REALITY?

Date: Tuesday, June 4 | | Time: 3:00 - 3:45pm | | DAC Pavilion - Booth 871 Keywords: Implementation, Emerging Technologies | | Topic Area: Design, EDA

MODERATOR: ORGANIZER:

Dr. Prith Banerjee - ANSYS, Inc., San Jose, CA

Vic Kulkarni - ANSYS, Inc., San Jose, CA

#### **DAC BINGO**

Date: Tuesday, June 4 | | Time: 4:30 - 5:00pm | | DAC Pavilion - Booth 871

Wednesday, June 5

# DEEP LEARNING MEETS SILICON - A PROGRESS REPORT ON TECHNOLOGY, APPLICATIONS, STARTUPS AND CHALLENGES

Date: Wednesday, June 5 | Time: 10:30 - 11:15am | DAC Pavilion - Booth 871

SPEAKER: Chris Rowen - Babblelabs, Inc., San Jose, CA

### ELECTRONICS INNOVATION'S GREAT LEAP FORWARD: AN OVERVIEW OF THE JUMP PROGRAM

Date: Wednesday, June 5 | | Time: 11:30am - 12:00pm | | DAC Pavilion - Booth 871

ORGANIZER: Anand Raghunathan - Purdue Univ., Fort Wayne, IN

## RISC-V OPPORTUNITIES AND CHALLENGES IN AN "OPEN" TECHNOLOGY SOCIETY

Date: Wednesday, June 5 | Time: 2:00 - 2:45pm | DAC Pavilion - Booth 871

**MODERATOR:** Ed Sperling - Semi Engineering

#### **HACK@DAC - LIVE DEMO/MIRAI ATTACK**

Date: Wednesday, June 5 | Time: 3:00 - 5:00pm | DAC Pavilion - Booth 871

ORGANIZER: Ahmad Reza Sadeghi - Technische Univ. Darmstadt

| Keynotes  | SKY Talks                | Research Sessions | Designer/IP<br>Track Sessions | Panels     | DAC Pavilion     | Monday Tutorials |

|-----------|--------------------------|-------------------|-------------------------------|------------|------------------|------------------|

| Workshops | Thursday is Training Day | Poster Sessions   | Additional Meetings           | Networking | Special Sessions | Design-on-Cloud  |

# SULAY, JUNE 2

W<sub>1</sub>

### WORKSHOP 1: STORAGE PROFILING, CONTAINERIZATION AND CLOUD FOR EDA

Time: 8:00am - 5:00pm | | Room: N253 | | Event Type: Workshop Keywords: Emerging Technologies | | Topic Area: EDA

#### **ORGANIZER:**

**Derek Magill** - The Association of High Performance Computing Professionals, Austin, TX

New and exciting IT infrastructure technologies are widely gaining adoption outside of EDA. This workshop focuses on some core capabilities needed by EDA companies in order to begin to embrace these new technologies. In this day-long course, we will cover:

Storage Profiling utilizing Ellexus (90 minutes)

- Tracing application dependencies in detail to provide a bill of materials showing all the locations a flow requires in order to run

- Collecting system-wide telemetry on storage performance of the above flow

- Finding applications that have I/O problems or what type of I/O patterns are likely to cause problems

How to size storage for Cloud for huge cost savings using Singularity Containers (90 minutes)

- · Introduction to containers and Singularity containers specifically

- Performance and security considerations when selecting a container technology

How to containerize an application for portability using Singularity EDA on AWS (60 minutes)

Running Scale-Out Engineering Workloads on the Cloud using Rescale (120 minutes)

- The attraction of running engineering workloads on the cloud is the promise of scale. However, running workloads at scale securely in the cloud often requires complicated set-up and development.

- This workshop will cover how to set-up and run a scale-out engineering workload on Rescale's turnkey platform.

- We will review how to monitor the job progress, set limits and budgets, and review results.

\*\*Registered attendees are requested to bring their laptops to this workshop

#### SPEAKERS:

Rosemary Francis - Ellexus. Cambridge, United Kingdom Gregory Kurtzer - Sylabs.io, San Francisco, CA Richard Paw - Rescale, Inc., San Francisco, CA Riaz Liyakath - Rescale, Inc., San Francisco, CA

**W2**

# WORKSHOP 2: CEDA WORKSHOP ON CAD FOR SAFE AND SECURE ELECTRONIC SYSTEM DESIGN

Time: 8:00am - 5:00pm | | Room: N255 | | Event Type: Workshop Keywords: Architecture & System Design, Test/Manufacturing/Reliability/Safety Topic Area: Embedded Systems & Software (ESS), Security

#### **ORGANIZERS:**

Francesco Regazzoni - Univ. of Lugano, Switzerland Marilyn Wolf - Georgia Institute of Technology, Atlanta, GA

Safe and secure electronic systems have become an important priority for industry, government, and consumers. Cyber-physical systems and Internet-of-Things (IoT) systems rely on safe and secure electronic systems. These systems are only as secure as the CAD tools used to create them. This workshop will explore the requirements on CAD systems for safety and security and the methodologies and algorithms required to satisfy these requirements.

Both the goals of safety/security and the best techniques to achieve these goals are rapidly evolving. Standards and certification are two complementary mechanisms for safe and secure system design. Standards provide both goals and processes; certification is a regulatory process that is used in some domains. Externally-defined safety/security goals for CAD tools are relatively new; methodologies and algorithms to produce and use these tools are still evolving.

The workshop will draft a report identifying goals and research issues.

Topics of interest to the workshop include but are not limited to:

- Certification and validation of CAD tools.

- · Secure design flows and design information integrity.

- Integrity of intellectual property.

- Attack models on electronic system hardware and software.

- CAD to secure against side channel attacks.

- Implications of existing security and safety standards on CAD.

- Embedded software design for safe and secure systems.

- Design of privacy-ensuring systems.

- Safe and secure CAD for cyber-physical control systems.

- Safe and secure CAD for wide-area IoT systems.

Participants may submit a 1-page white paper to wolf@ece.gatech.edu for participation as a poster and five-minute presentation.

#### **SPEAKERS:**

Marilyn Wolf - Georgia Institute of Technology, Atlanta, GA Francesco Regazzoni - Univ. of Lugano, Switzerland

| Keynotes  | SKY Talks                | Research Sessions | Designer/IP<br>Track Sessions | Panels     | DAC Pavilion     | Monday Tutorials |

|-----------|--------------------------|-------------------|-------------------------------|------------|------------------|------------------|

| Workshops | Thursday is Training Day | Poster Sessions   | Additional Meetings           | Networking | Special Sessions | Design-on-Cloud  |

W3

### WORKSHOP 3: GRAND CHALLENGES AND RESEARCH TOOLS FOR QUANTUM COMPUTING

Time: 8:00am - 12:00pm | | Room: N257 | | Event Type: Workshop | | Keywords: Architecture & System Design, Emerging Technologies, Verification/Validation Topic Area: Design, EDA

#### **ORGANIZERS:**

Diana Franklin - Univ. of Chicago, IL

Ali Javadi-Abhari - IBM T.J. Watson Research Center, White Plain, NY

We offer this workshop to grow an urgently needed community of computer science researchers for quantum computing. Speakers will be a combination of PIs from the EPiQC project, an NSF Expedition in computing, and researchers from IBM's quantum computing group. We will introduce and discuss areas of research in quantum computing where computer science contribution is most needed. We will also introduce an

end-to-end infrastructure for conducting quantum computing research based upon EPiQC's Scaffold tools and IBM's Qiskit tools. Participants will have the opportunity to run code on IBM's real quantum hardware through their cloud service, which will be exclusively reserved for the duration of the workshop.

#### **SPEAKERS:**

Diana Franklin - Univ. of Chicago, IL

Ali Javadi-Abhari - IBM T.J. Watson Research Center, White Plain, NY

W4

# WORKSHOP 4: THE FOURTH INTERNATIONAL WORKSHOP ON DESIGN AUTOMATION FOR CYBER-PHYSICAL SYSTEMS (DACPS)

Time: 8:00am - 5:00pm | | Room: N261 | | Event Type: Workshop | | Keywords: IoT, Automotive, Security & Privacy | | Topic Area: Embedded Systems & Software (ESS), EDA

#### **CHAIR:**

Mohammad Al Faruque - Univ. of California, Irvine, CA

#### **CO-CHAIR:**

Chung-Wei Lin - National Taiwan Univ., Taiwan

#### **ORGANIZERS:**

Miroslav Pajic - Duke Univ., Durham, SC

Shiyan Hu - Michigan Technological Univ., Houghton, Ml

Xin Li - Duke Univ., Durham, NC

Sandip Ray - Univ. of Florida, Gainesville, FL

Bei Yu - Chinese Univ. of Hong Kong

Umit Ogras - Arizona State Univ., Tempe, AZ

Huafeng Yu - Boeing, Ladson, SC

Qi Zhu - Northwestern Univ., Evanston, IL

Yier Jin - Univ. of Florida, Gainesville, FL

Bei Yu - Chinese Univ. of Hong Kong

Paul Bogdan - Univ. of Southern California, Los Angeles, CA

Phillip Brisk - Univ. of California, Riverside, CA

Dip Goswami - Eindhoven Univ. of Technology, Netherlands Antilles

Cyber-Physical Systems (CPS) are characterized by the strong interactions between cyber and physical components. CPS system examples include automotive and transportation systems, avionics systems, smart home, building and community, smart battery and energy systems, robotic systems, cyber-physical biochip, wearable devices, and so on. Due to the deeply complex intertwining among different components, CPS designs pose fundamental challenges in multiple aspects such as safety, performance, security, reliability, fault tolerance, extensibility, and energy consumption. Developing innovative design automation techniques, algorithms and tools is imperative to address the unique challenges in CPS design and operation, such as the fast increase of system scale and complexity, the close interactions with dynamic physical environment and human activities, the significant uncertainties in sensor readings,

the employment of distributed architectural platforms, and the tight resource and timing constraints. This workshop will present the state-of-the-art research results on the topic of design automation for CPS/IoT systems, introduce practical challenges and promising solutions in various industry sectors, and stimulate CAD researchers to participate in the interdisciplinary CPS/IoT research. In addition to the regular submissions, this workshop will also seek invited submissions/talks from high-profile experts in both academia and industry.

#### **SPEAKERS:**

Sanjit Seshia - Univ. of California, Berkeley, CA

Arquimedes Canedo - Siemens Corp., Princeton, NJ

Sukamo Mertoguno - Office of Naval Research, Scotts Valley, CA

Valeriy Sukharev - Mentor, A Siemens Business, Fremont, CA

Umit Ogras - Arizona State Univ., Tempe, AZ

**Bei Yu** - Chinese Univ. of Hong Kong **Xun Jiao** - Villanova Univ., Villanova, PA

Wanli Chang - Univ. of York, United Kingdom

Pierluigi Nuzzo - Univ. of Southern California, Los Angeles, CA

Houssam Abbas - Oregon State Univ., Corvallis, OR

Francesco Regazzoni - Univ, of Lugano, Advanced Learning and Research Institute. Switzerland

Shivam Bhasin - Nanyang Technological Univ., Singapore

Miroslav Pajic - Duke Univ., Durham, SC

Muhammad Shafique - Technische Univ. Wien, Austria

Sandip Ray - Univ. of Florida, Gainesville, FL Phillip Brisk - Univ. of California, Riverside, CA Yier Jin - Univ. of Florida, Gainesville, FL

| Keynotes  | SKY Talks                | Research Sessions | Designer/IP<br>Track Sessions | Panels     | DAC Pavilion     | Monday Tutorials |

|-----------|--------------------------|-------------------|-------------------------------|------------|------------------|------------------|

| Workshops | Thursday is Training Day | Poster Sessions   | Additional Meetings           | Networking | Special Sessions | Design-on-Cloud  |

**W5**

### WORKSHOP 5: BRIDGING THE GAP BETWEEN ARTIFICIAL TO NATURAL INTELLIGENCE

Time: 8:30am - 5:00pm || Room: N259 || Event Type: Workshop Keywords: Architecture & System Design, Emerging Technologies, Analog & Mixed Signal || Topic Area: Machine Learning/AI, Design

#### **ORGANIZERS:**

Jae-sun Seo - Arizona State Univ., Tempe, AZ Arijit Raychowdhury - Georgia Institute of Technology, Atlanta, GA

Despite tremendous progress in recent deep learning algorithms and hardware, there still exists three to four orders of energy efficiency gap between artificial and natural intelligence. Towards bringing this gap, upto-date results of neuroscience needs to be abstracted to the algorithmic level, so that they can be implemented in engineering solutions. Based on understanding how the brain works, engineers from various disciplines need to collaborate on learning algorithms, knowledge representation, and architectures.

The objective of this workshop is to bring together researchers from across the JUMP (Joint University Microelectronics Program, funded by SRC and DARPA) community to discuss the most promising approaches towards the overarching goal of bridging the energy efficiency gap between artificial and natural intelligence. The workshop will explicitly focus on approaches that are well beyond today's deep neural networks and neural network accelerators.

Topics of interest will include bio-inspired network models and learning algorithms, neuro-mimetic devices and circuits, and hardware that embodies the information processing principles of the brain. Exemplary research efforts from both academia and industry will be presented. The workshop aims to establish a forum to discuss the current practices, as well as future research needs in the corresponding fields.

#### **SPEAKERS:**

Kaushik Roy - Purdue Univ., West Lafayette, IN

Laurent Itti - Univ. of Southern California, Los Angeles, CA

**David Brooks** - Harvard Univ., Cambridge, MA **Mike Davies** - Intel Corp., Hillsboro, OR

Anand Raghunathan - Purdue Univ., West Lafayette, IN

Jae-sun Seo - Arizona State Univ., Tempe, AZ

Shimeng Yu - Georgia Institute of Technology, Atlanta, GA

Arijit Raychowdhury - Georgia Institute of Technology, Atlanta, GA

Geoffrey Burr - IBM Research, San Jose, CA Suman Datta - Univ. of Notre Dame, Notre Dame, IN

W6

### WORKSHOP 6: NIM - WORKSHOP ON NEAR- AND IN-MEMORY COMPUTING TRENDS

Time: 1:00 - 5:00pm | | Room: N257 | | Event Type: Workshop Keywords: Emerging Technologies | | Topic Area: Design, Machine Learning/Al

#### **ORGANIZERS:**

Valeria Bertacco - Univ. of Michigan, Ann Arbor, MI David Brooks - Harvard Univ., Cambridge, MA

Near- and in-memory computing approaches are under intense exploration by researchers at the device, circuit, and architecture levels. This workshop will engage academic and industrialist to discuss current solutions, their applications and future trends in this space. The research span is quite broad covering a variety of topics and approaches. Because of the breadth of the research approach and the need to span multiple

layers of the technology stack, researchers at different levels often have difficulty comparing their approaches with others. The proposed workshop will bring together experts from multiple levels of the design stack, multiple institutions, and semiconductor companies to discuss a path forward in establishing the viability of in- and near-memory computing solutions over the next decade.

#### **SPEAKERS:**

Valeria Bertacco - Univ. of Michigan, Ann Arbor, MI David Brooks - Harvard Univ., Cambridge, MA

| Keynotes  | SKY Talks                | Research Sessions | Designer/IP<br>Track Sessions | Panels     | DAC Pavilion     | Monday Tutorials |

|-----------|--------------------------|-------------------|-------------------------------|------------|------------------|------------------|

| Workshops | Thursday is Training Day | Poster Sessions   | Additional Meetings           | Networking | Special Sessions | Design-on-Cloud  |

#### **DESIGN AUTOMATION SUMMER SCHOOL**

Time: 7:30am - 6:00pm | | Room: N250 | | Event Type: Additional Meeting Keywords: Architecture & System Design | | Topic Area: EDA

The Design Automation Summer School (DASS) is a one-day intensive course on research and development in design automation (DA). Each topic in this course will be covered by a distinguished speaker who will define the topic, describe recent accomplishments, and indicate remaining challenges. This program is intended to introduce and outline emerging challenges, and to foster creative thinking in the next generation of EDA engineers.

The 2019 SIGDA Design Automation Summer School is co-hosted by A. Richard Newton Young Fellowship Program at DAC. All the students receiving the fellowship (excluding the mentors) are required to attend DASS event.

For additional details go to: http://www.sigda.org/dass

Thank you to our Sponsors:

### A. RICHARD NEWTON YOUNG FELLOW PROGRAM WELCOME BREAKFAST & ORIENTATION

Time: 7:30 - 9:00am | | Room: N250 | | Event Type: Additional Meeting Topic Area: EDA

The Newton Young Fellow Program is designed to assist young students at the beginning of a career in Electronic Design Automation and Embedded Systems. Each Newton Young Fellow will actively engage in DAC through a number of events including meetings with design automation luminaries, attendance at technical sessions and exhibits, participation in student-related events at DAC.

In addition, Newton Young Fellows will participate in a welcome orientation breakfast on Sunday morning, attend the Design Automation Summer School program, present posters of their academic/research work on Tuesday evening (colocated with the SIGDA Ph.D. Forum), and participate in a closing award ceremony for Young Fellows on Thursday evening.

Following a 50-year tradition, DAC strives to foster a vibrant and worldwide community of electronic design and embedded systems professionals; the fellowship actively supports and attempts to build an active cohort of the next generation of EDA and Embedded Systems professionals.

**Welcome Breakfast and Orientation**

Sunday, June 2 7:30 - 9:00am Room: N250

Dr. Tom Williams Talk

Monday, June 3 3:00 - 4:00pm Room: N249

Poster Presentation (colocated with the Ph.D. Forum)

Tuesday, June 4 7:00 - 9:00pm Room: N246

**Closing Session and Award Ceremony**

Thursday, June 6 6:00 - 6:45pm

Room: N259

Thank you to our Corporate Sponsor:

cādence<sup>®</sup>

#### **ACM SIGDA/IEEE CEDA EARLY CAREER WORKSHOP AT DAC**

Time: 8:30am - 6:00pm || Room: N254 || Event Type: Additional Meeting Topic Area: Design, EDA

This workshop is for young and mid-career faculty and professionals in the fields related to electronic design automation (EDA). The workshop will start in the morning with an interactive session borrowing techniques from IMPROV to help you improve your soft skills (interpersonal, communication etc.) with others. This is followed by presentations and panel discussions by professionals discussing diverse topics such as navigating the various challenges to better succeed and thrive in your academic or industry

job, getting your projects funded and climbing academic and technical ladders, as well as improved cooperation between industry and academia research and development. In addition, the workshop will provide rich opportunities to closely interact and network with some of the established academicians, professionals, and funding officers in EDA related fields.

Thank you to our Corporate Sponsor: Thank you to our DAC Sponsors:

| Keynotes  | SKY Talks                | Research Sessions | Designer/IP<br>Track Sessions | Panels     | DAC Pavilion     | Monday Tutorials |

|-----------|--------------------------|-------------------|-------------------------------|------------|------------------|------------------|

| Workshops | Thursday is Training Day | Poster Sessions   | Additional Meetings           | Networking | Special Sessions | Design-on-Cloud  |

#### HACK@DAC FINAL COMPETITION

Time: 8:00am - 5:00pm | | Room: N256 | | Event Type: Additional Meeting Keywords: Architecture & System Design, Contest | | Topic Area: Security, Design

System-on-a-Chip (SoC) designers use third-party intellectual property (3PIP) cores and in-house IP cores to design SoCs. Trustworthiness of SoCs can be undermined by security bugs that are unintentionally introduced during the integration of the IPs. A security weakness, if discovered and exploited when the chips are in the field, can result in a compromise or bypass of one or more product security objectives. For example, an exploited security bug may lead to a deadlock or failure of the system, or create a backdoor through which an attacker can gain remote access to leak secrets from the system. The goal of this competition is to develop tools and methods for identifying security vulnerabilities in buggy SoCs.

In this 33-hour ordeal, the top scoring teams from phase I of the competition will compete live to find and report security bugs from an SoC that is released to them at the start of the day. These teams mimic the role of a security research team at the SoC integrator, as try to find the security vulnerabilities and report them back to the design team quickly, so they can be addressed before the SoC goes to market. The bug submissions from the participating teams are scored in real time by an expert team from industry and academia.

#### **EDA OBSERVATIONS AND OUTLOOK: A WALL STREET PERSPECTIVE**

Date: Sunday, June 2 | | Time: 5:30 - 6:00pm | | Room: Westgate Hotel - Ballroom B Event Type: Additional Meeting

Richard F. Valera - Managing Director, Equity Research Needham & Company, New York, NY This talk will explore the design software industry from the perspective of a Wall St. analyst.

Topics covered will include industry consolidation, growth rates, vertical market drivers, investment and public company stock performance.

#### WELCOME RECEPTION

**Sunday, June 2 6:00 - 7:30pm | Westgate Hotel - Ballroom A**Join fellow attendees for the first event to network and kick-off DAC 2019

Music courtesy of:

| Keynotes  | SKY Talks                | Research Sessions | Designer/IP<br>Track Sessions | Panels     | DAC Pavilion     | Monday Tutorials |

|-----------|--------------------------|-------------------|-------------------------------|------------|------------------|------------------|

| Workshops | Thursday is Training Day | Poster Sessions   | Additional Meetings           | Networking | Special Sessions | Design-on-Cloud  |

# MONDAY, JUNE 3

#### **OPENING SESSION & AWARDS PRESENTATION**

Time: 8:45 - 9:00am | | Keynote Booth 1145

Join us as we set the stage for the 56th DAC! DAC's Executive Committee will highlight the conference's events, and the award presentations will recognize success and excellence for individuals in the field of design automation of electronic systems.

#### 2018 PHIL KAUFMAN AWARD FOR DISTINGUISHED CONTRIBUTIONS TO ELECTRIC SYSTEMS DESIGN Thomas W. Williams, Consultant, Synopsys (retired), Synopsys Fellow

For Overall Impact on Electronics Industry through Contributions to Scan Design for Testability, Related Test Automation

### ACM IEEE A. RICHARD NEWTON TECHNICAL IMPACT AWARD IN ELECTRONIC DESIGN AUTOMATION

Edward B. Eichelberger, IBM (retired) IBM Fellow, IEEE Fellow Thomas W. Williams, Consultant, Synopsys (retired), Synopsys Fellow

For the paper "A Logic Design Structure for LSI Testability," In Proc. of the 14th Design Automation Conference, 1977

### 2019 MARIE R. PISTILLI WOMEN IN ENGINEERING ACHIEVEMENT AWARD

Iris Bahar - Professor of Engineering and Computer Science, Brown Univ.

#### P.O. PISTILLI UNDERGRADUATE SCHOLARSHIP FOR ADVANCEMENT IN COMPUTER SCIENCE AND ELECTRICAL ENGINEERING

**Gia Douglass**

#### **DAC UNDER-40 INNOVATORS AWARD**

The Under-40 Innovators Award is sponsored by Association for Computing Machinery (ACM), and the Institute of Electrical and Electronics Engineers (IEEE). The award will recognize the top five young innovators (nominees should be 40 years or younger in age as of June 1, 2019) who are movers and shakers in the field of design and automation of electronics.

#### **SYSTEM DESIGN CONTEST WINNERS**

#### **HACK@DAC WINNERS**

### VISIONARY TALK: GAME CHANGERS: HOW AUTOMATION HAS CHANGED THE GAMING INDUSTRY

Monday, June 3 | 9:00 - 9:20am | Keynote Booth 1145

In the last 30 years, automation has changed the operation of casinos to a greater extent than in the 3,000 year history of the industry. Beginning with a quick overview of what constitutes innovation, two very important examples of the application of automation to the industry will be given. These two innovations alone account for multi-billion dollar increases in revenue. Finally, several of

the latest trends in gaming innovation will be presented, with an open invitation to the audience to explore the application of automation in these areas.

#### SPEAKER:

Mark Yoseloff, Ph.D. - Executive Director, UNLV Center for Gaming Innovation, Univ. of Nevada, Nevada Las Vegas

# **KEYNOTE:** SECURING THE BILLIONS OF DEVICES AROUND US

**GALEN C. HUNT** – Distinguished Engineer and Managing Director, Microsoft Corporation, Redmond WA

Time: 9:20 - 10:00am | | Keynote Booth 1145

The next decade promises the democratization of connectivity to every device. Significant drops in the cost of

connectivity mean that every form of electrical device—every child's toy, every household's appliances, and every DoD sensor—will become connected to the Internet. Tens of billions of these devices are controlled by microcontrollers, a class of device particularly ill-prepared for the security challenges of internet connectivity. What is required to secure these billions of devices? And, how can it be done economically enough to apply to every device?

**Biography:** Dr. Galen Hunt founded and leads the Microsoft team responsible for Azure Sphere. Their mission is to ensure that every IoT device on the planet is secure and trustworthy. Previously, Dr. Hunt pioneered technologies ranging from confidential cloud computing to light-weight container virtualization, type-safe operating systems, and video streaming. Dr. Hunt was a member of Microsoft's founding cloud computing team. Dr. Hunt holds over 100 patents, a B.S. degree in Physics from University of Utah and Ph.D. and M.S. degrees in Computer Science from the University of Rochester.

DT1

#### IS YOUR AI-BASED EDA TOOL PRODUCTION-READY?

Time: 10:30am - 12:00pm | | Room: N260 | | Event Type: Designer Track Keywords: Front-end Design, Back-end Design, Low Power | | Topic Area: Machine Learning/AI, EDA

#### **MODERATOR:**

John Ellis - Silicon Integration Initiative, Inc., Austin, TX

#### **ORGANIZER:**

Leigh Anne Clevenger - Silicon Integration Initiative, Inc., Austin, TX

Artificial intelligence-based design automation algorithms tested in research studies show improved runtime and inference results over traditional EDA approaches. What does it take to move machine learning, deep learning, and reinforcement learning from research feasibility studies to production-worthy AI design automation tools?

For Al-based EDA tools, this panel discussion will explore the following:

- How do we feed the Al beast? What data is needed? Where does it come from and what relationships are required?

- What software platforms are available today to move research-level prototypes to production-level flows?

- Can research-level systems be successfully used in-house to improve hardware and software training and inference solutions? What criteria would necessitate a transition to production level?

- What I/O and data structure standards are needed to enable different Al engines for training and inference, shared Al models, and state-ofthe-art visualization tools

#### **PANELISTS:**

Rhett Davis - North Carolina State Univ., Raleigh, NC Leon Stok - IBM Systems Group, Poughkeepsie, NY Ramy Iskander - Intento Design, Paris, France Leigh Anne Clevenger - Silicon Integration Initiative, Inc., Austin, TX

Thank you to our Designer Track Sponsor:

DT2

#### **NEW FRONTIERS IN FORMAL AND STATIC VERIFICATION**

Time: 10:30am - 12:00pm | Room: N262 | Event Type: Designer Track Keywords: Verification/Validation, Front-end Design, Low Power | Topic Area: EDA, Design

#### **CHAIR:**

Maheshwar Chandrasekar - Synopsys, Inc., Sunnyvale, CA

Formal Verification continues to be one of the fastest-growing categories in EDA, with increasing recognition that it has hit a level of maturity where any modern design team needs to leverage it to stay competitive. The presentations in this session will help your team to stay abreast of the latest developments in formal and related technologies, and provide ideas to raise your design and validation process to the next level.

#### 2.1 Stop Leaking Unverified Corner Cases

Wayne Yun - Advanced Micro Devices, Inc., Markham, ON, Canada

### **2.2 Bug Hunting for Deep Sequential Complex S/M using Formal Nitin M. Mhaske**, *Synopsys, Inc., Austin, TX*

Iain Singleton - Synopsys, Inc., Mountain View, CA

### 2.3 Achieving Sign-off Efficiently Via Static Verification Tools Customized for High-value Failure Modes

Akitsugu Nakayama, Masashi Shibata, **Atsunori Machida**, Katsumi Imamura, Yuji Yoshitani - Fujitsu Kyushu Network Technologies Ltd., Fukuoka, Japan

2.4 Unbounded Formal Verification of RISC-V CSRs with Interval Property Checking

**Nicolae Tusinschi**, Sven Beyer - *OneSpin Solutions GmbH*, *Munich, Germany*

2.5 CDC Handshake: Advanced Sign-off Methodology

Ramakrishna Rayaprolu - NVIDIA Corp., Santa Clara, CA **Vikas Sachdeva** - Real Intent, Inc. Sunnyvale, CA Prakash Mukre, Louis Caradillo, Vivek Gupta - NVIDIA Corp., Santa Clara. CA

2.6 Deadlock & Livelock Detection in Power Controllers using Under-constrained Formal Testbench

Ipshita Tripathi, Arumugam Velayoudame, Rahul Gupta, Vinay Garipelli - Qualcomm India Pvt. Ltd., Bangalore, India

Thank you to our Designer Track Sponsor:

| Keynotes  | SKY Talks                | Research Sessions | Designer/IP<br>Track Sessions | Panels     | DAC Pavilion     | Monday Tutorials |

|-----------|--------------------------|-------------------|-------------------------------|------------|------------------|------------------|

| Workshops | Thursday is Training Day | Poster Sessions   | Additional Meetings           | Networking | Special Sessions | Design-on-Cloud  |

IP3

#### **HOW PAM4 AND DSP ENABLE 112G SERDES DESIGN**

Time: 10:30am - 12:00pm | | Room: N264 | | Event Type: IP Track Keywords: Architecture & System Design, Analog & Mixed Signal | | Topic Area: IP

#### **CHAIR & ORGANIZER:**

Eric Esteve - IP-nest, Marseille, France

Incredibly fast growing demand for bandwidth needed to support chip to chip and system to system communication is pushing the industry to develop very high speed SerDes, up to 112G (112 Gbps). In 2005, state of the art SerDes speed was 5 Gbps, moving to 10 Gbps in 2010 and 28 Gbps in 2014. New DSP-based techniques like Pulse Amplitude Modulation (PAM 4) enable the design of SerDes running at up to 112 Gbps. Join this session to hear the companies involved in very high speed SerDes IP design describe new architectures and techniques allowing them to reach data rates more than 20 times higher than in 2005.

- **3.1** How DSP is Killing the Analog in SerDes

Tony Pialis AlphaWave IP Corp., Toronto, ON, Canada

- 3.2 Enabling 400G/800G Interconnects with 56G/112G PAM-4 PHY

Rita Horner - Synopsys, Inc., Mountain View, CA

3.3 Boosting the 112G Performance with PAM4 DSP

Rishi Chugh - Cadence Design Systems, Inc., San Jose, CA

Thank you to our IP Track Sponsor:

### SKY TALK: WHAT CAN EDA DO FOR QUANTUM COMPUTING AND WHAT CAN QC DO FOR EDA?

Time: 1:00 - 1:45pm | DAC Pavilion - Booth 871 | Event Type: SKY Talk

Though early in its development, quantum computing is now available on real hardware via the cloud through IBM Q. This radically new kind of computing holds open the possibility of solving some problems that are now and perhaps always will be intractable for "classical" computers.

As with any new technology there are a lot of open questions. What is the road to Quantum

Advantage, e.g. the point where quantum computing shows demonstrable and significant advantage over classical computers and algorithms? What is the status of Quantum computers today? How do we define a full system-metric to measure the performance of a Quantum System? This

Skytalk will answer these questions. We will discuss what we can do in EDA to improve the performance of Quantum Systems and describe the types of EDA problems where quantum computing might be applied.

#### SPEAKER:

**Leon Stok** - Vice President of IBM's Electronic Design Automation Group, Poughkeepsie, NY

Thank you to our DAC Pavilion Sponsor:

| Keynotes  | SKY Talks                | Research Sessions | Designer/IP<br>Track Sessions | Panels     | DAC Pavilion     | Monday Tutorials |

|-----------|--------------------------|-------------------|-------------------------------|------------|------------------|------------------|

| Workshops | Thursday is Training Day | Poster Sessions   | Additional Meetings           | Networking | Special Sessions | Design-on-Cloud  |

DT4

#### **POWER BYTES DELIVERED**

Time: 1:30 - 3:00pm | | Room: N260 | | Event Type: Designer Track Keywords: Back-end Design, Low Power, Implementation | | Topic Area: Design, EDA

#### CHAIR:

Badhri Uppiliappan - Analog Devices, Inc., Norwood, MA

This session will begin with a journey into improving power analysis for large and complex multi-voltage, multi-chip; followed by deeper exploration of various aspects of building and analyzing power grid networks and electro-migration from signoff perspectives.

#### 4.1 Efficient Multi Power Domain Analysis using IPD Flow

**Jongyoon Jung** - Samsung Electronics Co., Ltd., Hwaseong-si, Republic of Korea

Aniket Deshmukh - Cadence Design Systems, Inc., Seongnam-Si, Republic of Korea

Pawan D. Gandhi - Cadence Design Systems, Inc. & BITS Pilani, Noida, India

Naresh Kumar - Cadence Design Systems, Inc., Uttar Pradesh, India Arvind Veeravalli, Ritika Govila - Cadence Design Systems, Inc., Bengaluru, India

Jeannette Sutherland - Cadence Design Systems, Inc., Austin, TX

#### 4.2 3D Stacked (Foveros) SOC Power Delivery Analysis Methodology for Predictable Silicon Success

**Biswajit Patra**, Ayan Roy Chowdhury - Intel Technology India Pvt. Ltd, Bangalore, India

### 4.3 Two Different Approaches of Power Integrity Analysis and Correlate with On-chip Measurement

Chee Kong Ung, Mizar Chang, Sean Hwang, Bihqui Tiang - MediaTek, Inc., Hsinchu City, Taiwan

PeiShen Wei, Ying-jiunn Lai, Chan Chiuan Lee - ANSYS, Inc., Taipei. Taiwan

Oscar Ou - MediaTek, Inc., San Jose, CA

# 4.4 Electro-migration Reliability Verification of Gate Level Blocks for High Performance Microprocessors in Presence of Selfheating

Nagu Dhanwada - IBM Corp., Poughkeepsie, NY Leon Sigal - IBM Research, Yorktown Heights, NY David Kadzov - IBM Systems Group, Williston, VT

### 4.5 A Multi-perspective Approach to IC Power Grid Development for 7nm Based Designs

Mahendrasing J. Patil, Ravi Teja Susarla, Surendra Boosam Kota - Intel Technology India Pvt. Ltd, Bangalore, India

#### 4.6 Electromigration Signoff based on IR-drop Degradation Assessment

Valeriy Sukharev, Mentor, A Siemens Business, Fremont, CA Armen Kteyan - Mentor, A Siemens Business, Yerevan, Armenia Jun-Ho Choy - Mentor, A Siemens Business, Fremont, CA Farid N. Najm - Univ. of Toronto, ON, Canada

Thank you to our Designer Track Sponsor:

DT5

### STOP WASTING YOUR VERIFICATION BUDGET - KNOW WHEN TO USE FORMAL

Time: 1:30 - 3:00pm | | Room: N262 | | Event Type: Designer Track Keywords: Verification/Validation, Front-end Design | | Topic Area: Design

#### CHAIR:

KiranKumar V.M. Achutha - Intel Corp., Bengaluru, India

#### **ORGANIZER**

Roger Sabbagh - Oski Technology, Inc., Ottawa, ON, Canada

How would you verify that your PCIe receiver framer never confused payload data with framing tokens or packet header symbols? Imagine exhaustively testing every possible combination of payload data, packet lengths, modes, link widths and framing errors.

Or, how about verifying that your GPU shader sequencer always fetched, decoded and resolved dependencies between instructions correctly, for all possible types and sequences of instructions – all while simultaneously accounting for exceptions, configuration changes, stalls and control flow events?

What about verifying the correct ordering of register accesses across a CPU pipeline with aggressive out-of-order speculation in the presence of exceptions and flushes?

These are designs with too many corner case scenarios to cover with random or directed test cases. Formal verification is needed to solve hard problems like these. In this session, we present application specific verification challenges and examples of how formal verification has been used to develop practical solutions.

#### 5.1 A Novel Approach to PCIe Receiver Framing Checks

Joe Keirouz - Broadcom Corp., San Jose, CA Vigyan Singhal - Oski Technology, Inc., San Jose, CA

#### 5.2 Formal Verification of a GPU Shader Sequencer

Vaibhav Tendulkar, Chirag Dhruv - Advanced Micro Devices, Inc., Santa Clara, CA

Ashutosh Prasad - Oski Technology, Inc., Gurgaon, India

#### 5.3 Effective Formal Solutions to CPU Verification Challenges

Vikram Khosa - Arm, Ltd., Austin, TX

Thank you to our Designer Track Sponsor:

| Keynotes  | SKY Talks                | Research Sessions | Designer/IP<br>Track Sessions | Panels     | DAC Pavilion     | Monday Tutorials |

|-----------|--------------------------|-------------------|-------------------------------|------------|------------------|------------------|

| Workshops | Thursday is Training Day | Poster Sessions   | Additional Meetings           | Networking | Special Sessions | Design-on-Cloud  |

IP6

#### **FUTURE AI TRENDS FOR IP WITHIN THE AUTOMOTIVE INDUSTRY**

Time: 1:30 - 3:00pm | | Room: N264 | | Event Type: IP Track Keywords: Automotive, Architecture & System Design | | Topic Area: IP

#### **MODERATOR:**

John Blyler - JB Systems, Portland, OR

#### **ORGANIZER:**

Nathan Mandelke - ChipEstimate.com, San Jose, CA

Artificial intelligence is quickly transforming and redefining the automotive industry in a multitude of ways. Over the past decade, we have seen such AI enhancements as driver assist, voice recognition, telecommunications (including Wi-Fi), cloud data connectivity, and autonomous cars. These advanced automotive features have created new opportunities and requirements for chip makers. From product innovation to compliance issues to various industry collaborations, IP innovation also comes with its various challenges. However, it not only can give automakers a competitive advantage, but also help a company stay ahead of the curve.

The future of AI in automotive is bright and seems to be limitless. Join this panel discussion about the impact of IP on the future direction of artificial intelligence in the automotive industry.

#### **PANELISTS:**

Dave Steer - Imagination Technologies Ltd., San Jose, CA

Charlie Janac - Arteris, Inc., San Jose, CA

Gordon Cooper - Synopsys, Inc., Mountain View, CA Steve Brightfield - Wave Computing, Campbell, CA

Ali Osman Ors - NXP Semiconductors, Ottawa, ON, Canada

Thank you to our IP Track Sponsor:

# INTEGRATE THE AWS CLOUD WITH RESPONSIVE XILINX MACHINE LEARNING AT THE EDGE

Time: 2:00- 4:00pm | | Room: N261 | | Event Type: Additional Meeting Topic Area: IP

#### **ORGANIZERS:**

Naveen Purushotham - Xilinx, San Jose, CA Kv Thanjavur Bhaaskar - Xilinx, San Jose, CA Hugo A. Andrade, Xilinx - San Jose, CA

In this meeting, learn how to integrate FPGA based low-latency edge machine learning with an IoT enabled distributed control application that leverages the massive scale of AWS Cloud analytics, Xilinx Edge Al based machine learning model deployment, application provisioning, and system dashboards. Based on a distributed industrial control scenario,

you will work through a hands-on integration of AWS Cloud services through AWS Greengrass on Zynq Ultrascale+ and Amazon FreeRTOS on Xilinx Zynq-7000 platforms. After this workshop, you will have a concrete understanding of how a distributed industrial control system makes use of AWS edge and cloud services plus how they enable the evolutionary approach to these types of long-lived systems towards an edge-to-cloud collaboration exemplified through the integration of machine learning applications at the industrial edge.

#### IEEE CEDA/ACM SIGDA ADVANCING DIVERSITY IN EDA (DivEDA) FORUM

Time: 2:00 - 6:00pm | | Room: N259 | | Event Type: Additional Meeting

Topic Area: EDA

#### **ORGANIZERS:**

Chengmo Yang - Univ. of Delaware, Newark, DE Ayse Coskun - Boston Univ., Boston, MA

The goal of the Advancing Diversity in EDA (DivEDA) event is to help facilitate women and underrepresented minorities (URM) to advance their careers in academia and industry, and hence, to help increase diversity in the EDA community. Through an interactive medium, our aim is to provide

practical tips to women and URM on how to succeed and overcome possible hurdles in their career growth, while at the same time, connecting senior and junior researchers to enable a growing diverse community, which will then help accelerate innovation in the EDA ecosystem and benefit societal progress.

Thank you to our Co-Sponsors:

| Keynotes  | SKY Talks                | Research Sessions | Designer/IP<br>Track Sessions | Panels     | DAC Pavilion     | Monday Tutorials |

|-----------|--------------------------|-------------------|-------------------------------|------------|------------------|------------------|

| Workshops | Thursday is Training Day | Poster Sessions   | Additional Meetings           | Networking | Special Sessions | Design-on-Cloud  |

DT7

### TINYML - ULTRA LOW POWER MACHINE LEARNING APPLICATIONS AND ARCHITECTURES

Time: 3:30 - 5:00pm | | Room: N260 | | Event Type: Designer Track Keywords: Architecture & System Design, Front-end Design, Low Power Topic Area: Design, Machine Learning/AI

#### **CHAIR & ORGANIZER:**

Ambar Sarkar - NVIDIA Corp., Santa Clara, CA

Machine learning represents a potent new computing model and is quickly spreading through almost every class of system - cloud, PC, mobile and IoT. But machine learning and deep neural networks have earned a reputation for huge computation loads, large memory footprint and high power. Can the industry find a way to adapt machine learning to the most power and cost sensitive applications?

This session explores the emerging concept of "Tiny ML" - hardware platforms, network structures, optimization methods and end applications that combine sophisticated learned inference models with minuscule power budgets. These systems, often aimed at power budgets as low a 1mW, carry great promise for smarter sensor swarms, autonomous systems with years of battery life and ubiquitous devices that add subtle intelligence to everyday interactions.

- 7.1 Ultra-low-power Command Recognition for Ubiquitous Devices Chris Rowen Babblelabs, Inc, Campbell, CA

- 7.2 Using Analog Computation in Flash Memory for Energyefficient Al Inference

- Manar El-Chammas Mythic, Redwood City, CA

- 7.3 Microwatts, Kilobytes, Megahertz, and Cents: Solving Real World Problems for Al at the Mobile Edge Scott Hanson - Ambig Micro, Austin, TX

Thank you to our Designer Track Sponsor:

DT8

#### **TIME SPACE CONTINUUM**

Time: 3:30 - 5:00pm | | Room: N262 | | Event Type: Designer Track Keywords: Back-end Design, Implementation | | Topic Area: Design, EDA

#### CHAIR:

Mike Kazda - IBM Systems and Technology Group, Poughkeepsie, NY

Improving timing closure by applying new perspectives to change the search space of solutions are some key messages that get explored in this session.

#### 8.1 Coverage Improvement of Assertion based SDC Verification at Early Design Phase

**Nozomi Yunokuchi** - Renesas Electronics Corp., Kodaira-shi, Japan

Himanshu Bhatnagar - Excellicon Inc., Laguna Hills, CA

### 8.2 Design Optimization and Implementation Methodology using Cells with Different Diffusion Breaks

Jae Hoon Kim, Yongdeok Kim, Wootae Kim, Hyung-Ock Kim, Joonyoung Shin - Samsung Electronics Co., Ltd., Hwaseong, Republic of Korea

Jaewon Lee - Samsung Semiconductor, Inc., Hwasung-si, Republic of Korea

Jung Yun Choi - Samsung Electronics Co., Ltd., Yong-in, Republic of Korea

### 8.3 An Advanced Method of Routing Optimization with 3D Coupling Aware to Improve Timing

Jialian Tang - Avera Semiconductor LLC & GLOBALFOUNDRIES, Shanghai, China

Baoguang Yan, Fengfeng Wu - Avera Semiconductor LLC & GLOBALFOUNDRIES, Beijing, China

Mike Trick - Avera Semiconductor LLC & GLOBALFOUNDRIES, Burlington, VT

#### 8.4 Local Layout Effect Aware Design Methodology for Performance Boost below 10nm FinFET Technology

Jae Hoon Kim, Wootae Kim, Naya Ha, Hyung-Ock Kim, Sunik Heo, Hyunjeong Roh - Samsung Electronics Co., Ltd., Hwaseong, Republic of Korea

Hayoung Kim - Siemens Corp., Hwaseong, Republic of Korea Yonghwan Kim, Hyunwoo Kim, Jung Yun Choi - Samsung Electronics Co., Ltd., Yong-in, Republic of Korea

### 8.5 A Graph based Modelling of Multi Input Switching (MIS) in STA with Silicon Path Frequency Correlation

Amartya Mazumdar, Ulhas Kotha, Anshuman Seth - NVIDIA

Corp., Bangalore, India

Tezaswi Raja - NVIDIA Corp., San Jose, CA

Reecha Jajodia, Jaison Kurien, Sarvesh Sharma - NVIDIA Corp., Bangalore, India

#### 8.6 Tile-based Automated Pipeline Floorplanning

Greg Ford - Avera Semiconductor LLC, Santa Clara, CA

Thank you to our Designer Track Sponsor:

| Keynotes  | SKY Talks                | Research Sessions | Designer/IP<br>Track Sessions | Panels     | DAC Pavilion     | Monday Tutorials |

|-----------|--------------------------|-------------------|-------------------------------|------------|------------------|------------------|